高電圧直流(HVDC)送電におけるモジュラーマルチレベルコンバータ(MMC)

MMC の主な用途の 1 つである高電圧 DC 電力伝送における MMC の使用のデモンストレーション。

導入

このアプリケーションノートでは、Typhoon HIL環境におけるモジュラー・マルチレベル・コンバータ(MMC)の活用例を紹介します。これを実証するために、MMCの主要な応用分野の一つであるHVDC(高電圧直流)送電アプリケーションにおけるMMCモデルの性能を示します。

モデルの説明

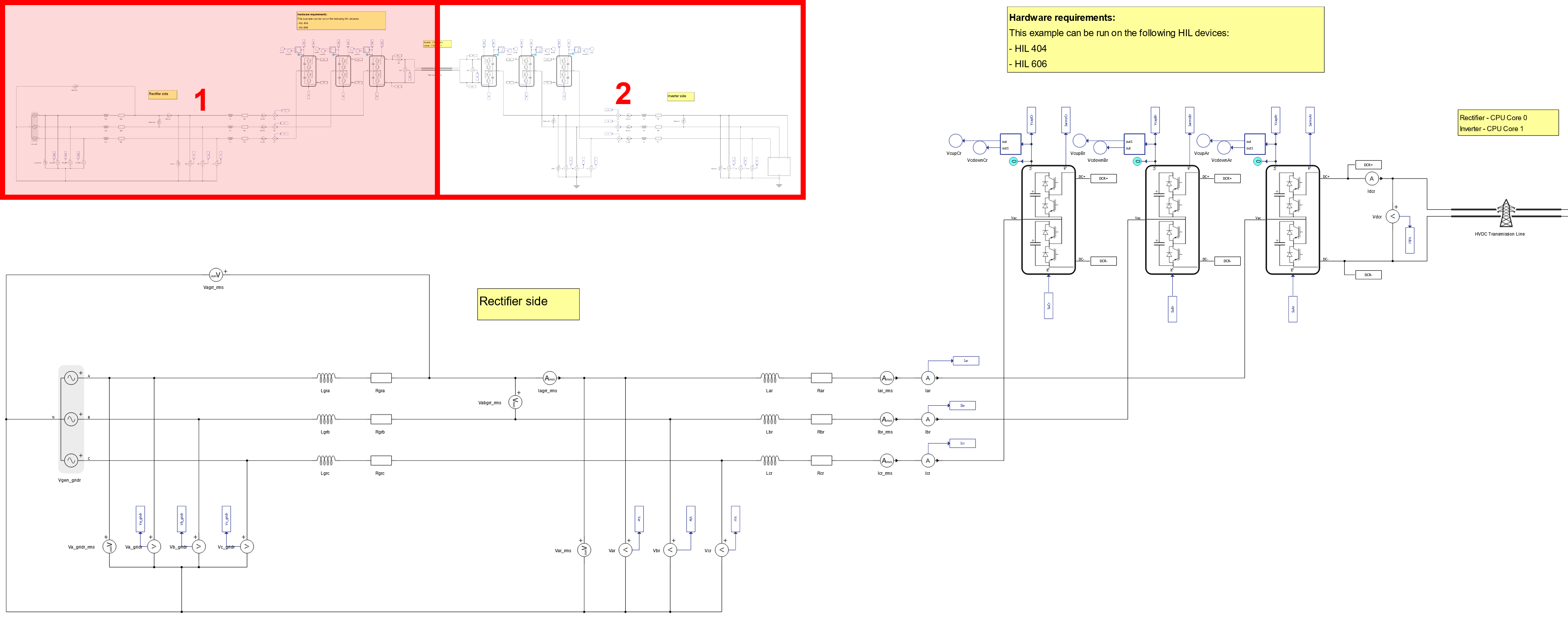

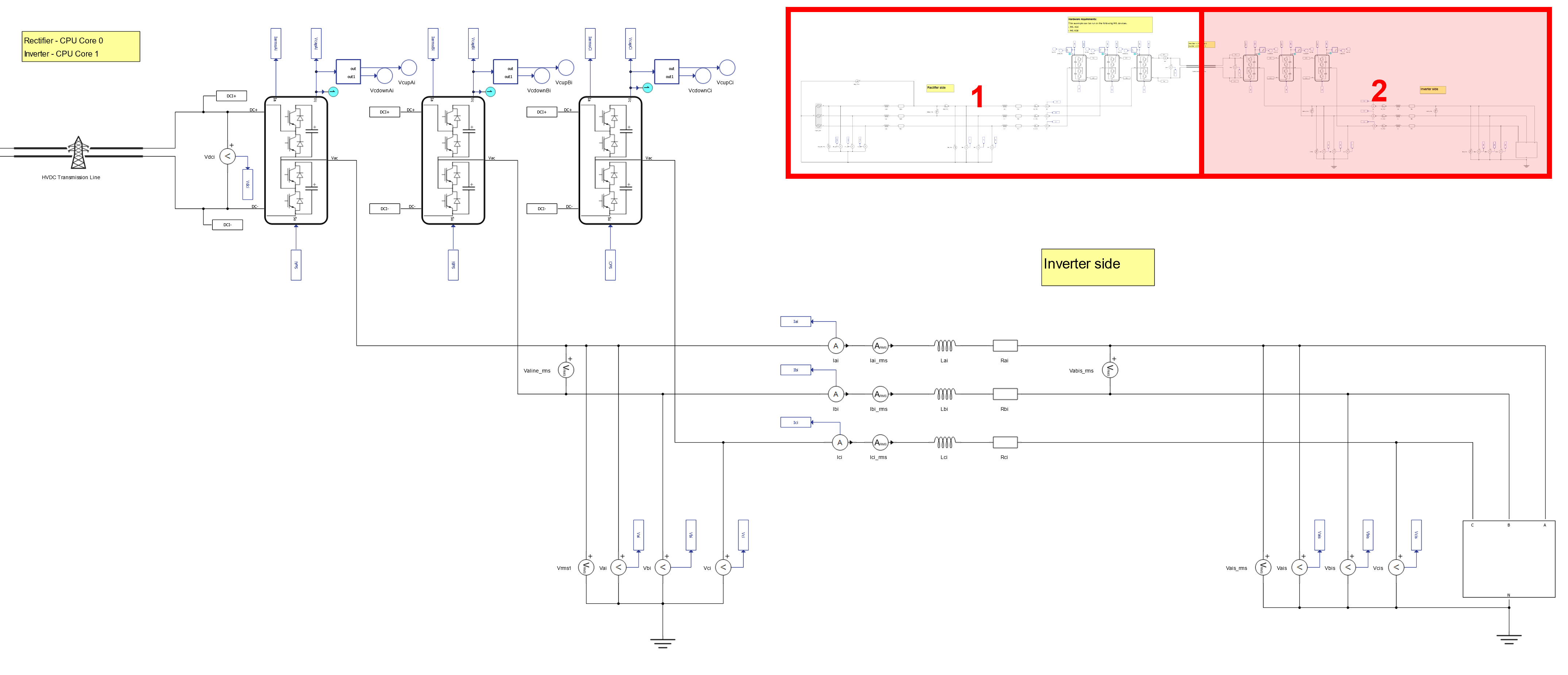

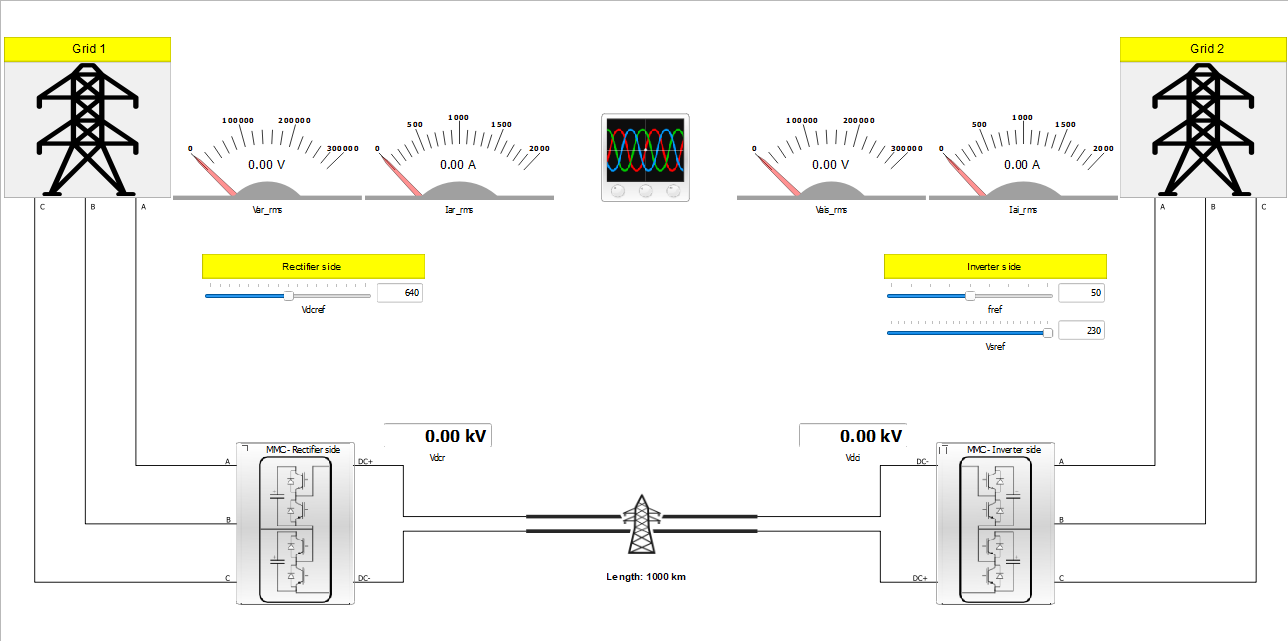

モデルには、6 つのモジュラー マルチレベル コンバータ (MMC) レグが含まれます。MMC の構造とトポロジの詳細については、「誘導機付きモジュラー マルチレベル コンバータ (MMC)」アプリケーション ノートの「概要」セクションを参照してください。モデルの左側にある 3 つの MMC レグは整流器として動作し、グリッドをエミュレートする 3 相電圧源 の 3 つの相のそれぞれに接続されます。グリッドの定格電圧は 230 kV、周波数は 50 Hz です。モデルのこの側は、整流器側と呼ばれます。モデルの右側にある 3 つの MMC レグはインバータとして動作し、定インピーダンス負荷の 3 つの相に接続されます。負荷の定格電圧は 230 kV、周波数は 60 Hz、定格電力は 1000 MVA です。モデルのこの側は、インバータ側と呼ばれます。2 つの側は、バックツーバック構成で接続されています。

MMCの整流器側DC出力は、HVDC送電線を介してMMCのインバータ側DC入力に接続されます。送電線の長さは1000 kmで、送電線にかかる公称DC電圧は640 kVです。電気モデルの整流器側を図1に示します。電気モデルのインバータ側を図2に示します。

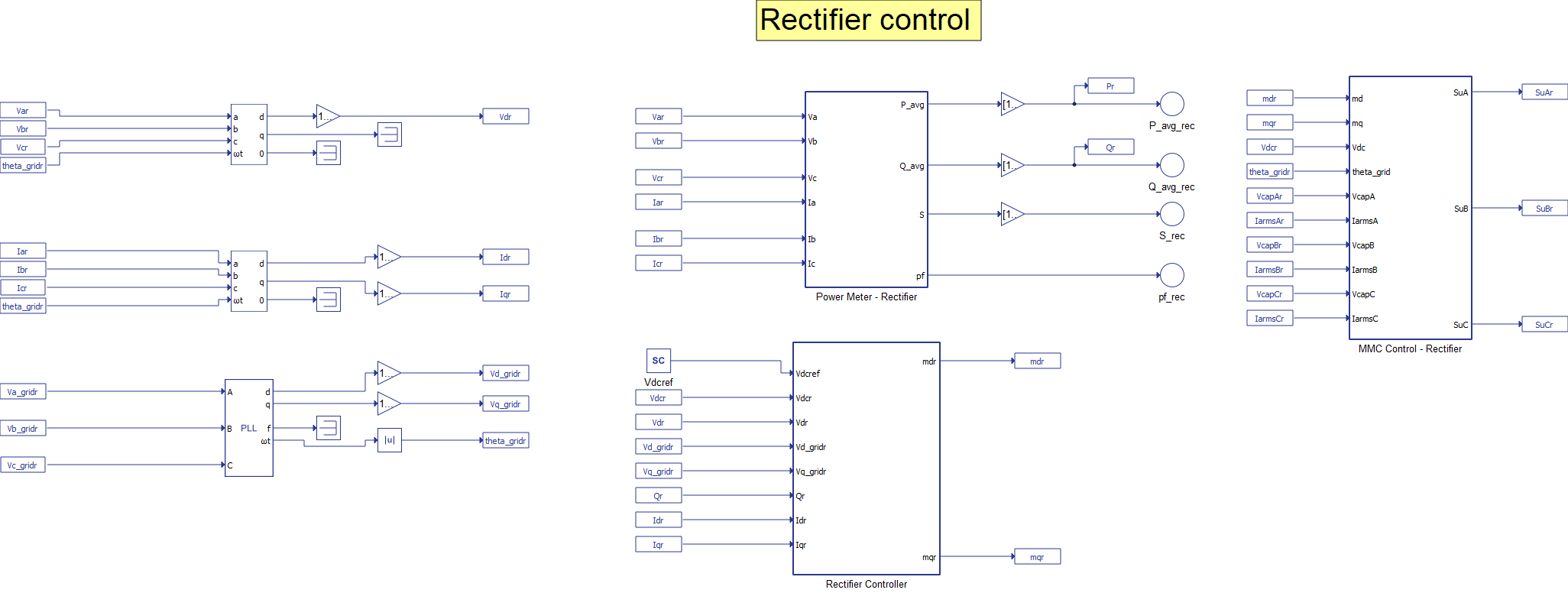

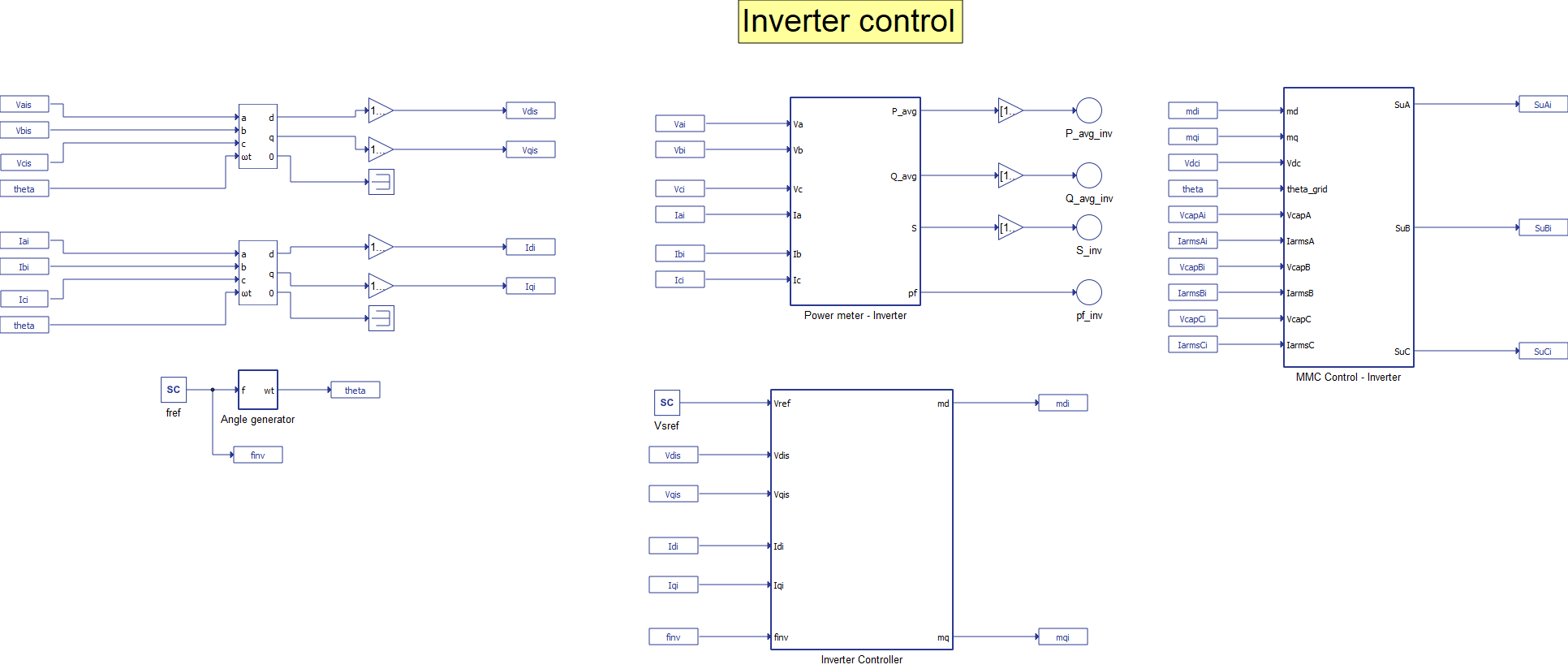

位相同期回路(三相PLL )とコンバーターの制御は、信号処理コンポーネントを使用して実装されています。MMCの制御は、 MMC制御 - 整流器サブシステムとMMC制御 - インバーターサブシステムに含まれるMMC Leg - NLC制御コンポーネントに実装されたNearest Level Control(NLC)を使用して管理されます。このモデルの階層数は17です。NLCブロックの適切なパラメータを変更することで、階層数を変更できます。

モデルの信号処理部分は、整流器制御アルゴリズムとインバータ制御アルゴリズムで構成されています。整流器側とインバータ側の制御アルゴリズムは閉ループとして実装され、それぞれ整流器コントローラサブシステムとインバータコントローラサブシステムに配置されています。制御用の参照値を提供するためにPLLコンポーネントが使用されます。信号処理の2つの部分を図3と図4に示します。

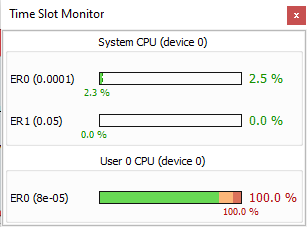

FPGAリソースを節約するため、MMCの電気モデルはスイッチング機能モデルに置き換えられました。スイッチング機能モデルは信号処理を使用して実装されています。つまり、MMCレベルの増加はCPU使用率の上昇につながり、計算間隔オーバーランにつながる可能性があります。HILのCPUを効率的に活用するために、モデルではCPUコアパーティショニングが使用されています。CPUマーカーは、信号処理モデルの一部を指定されたCPUコアにマッピングするために使用されます。CPUマーカーを使用することで、整流器側とインバータ側の信号処理部分(制御機能やスイッチング機能など)は、ユーザーCPUの別々のコアに分割されました。

シミュレーション

このアプリケーションには、図5に示すような、あらかじめ構築されたSCADAパネルが付属しています。このパネルには、実行時にシミュレーションを監視および操作するための、最も重要なユーザーインターフェース要素(ウィジェット)が用意されています。ニーズに合わせて自由にカスタマイズできます。

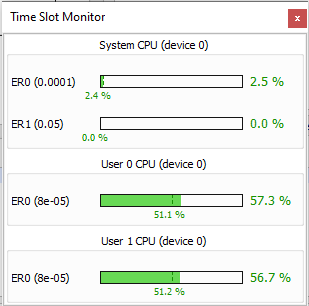

シミュレーション開始後、タイムスロットモニターを使用してCPU使用率を確認できます。図6は、モデルが単一のCPUコアで実行されている際のCPU使用率を示しています。このときの使用率は100%を超えており、計算間隔オーバーランを示すCIOフラグが設定されます。シミュレーション結果は不正確になります。

図7は、同じモデルを2つのコアで実行した場合のCPU使用率を示しています。両コアの使用率は約57%で、CIOフラグは設定されていません。これが、このケースでCPUマーカーの使用が必要な理由です。CPUマーカーが必要な理由の詳細については、電気回路のパーティショニングに関するドキュメントをご覧ください。

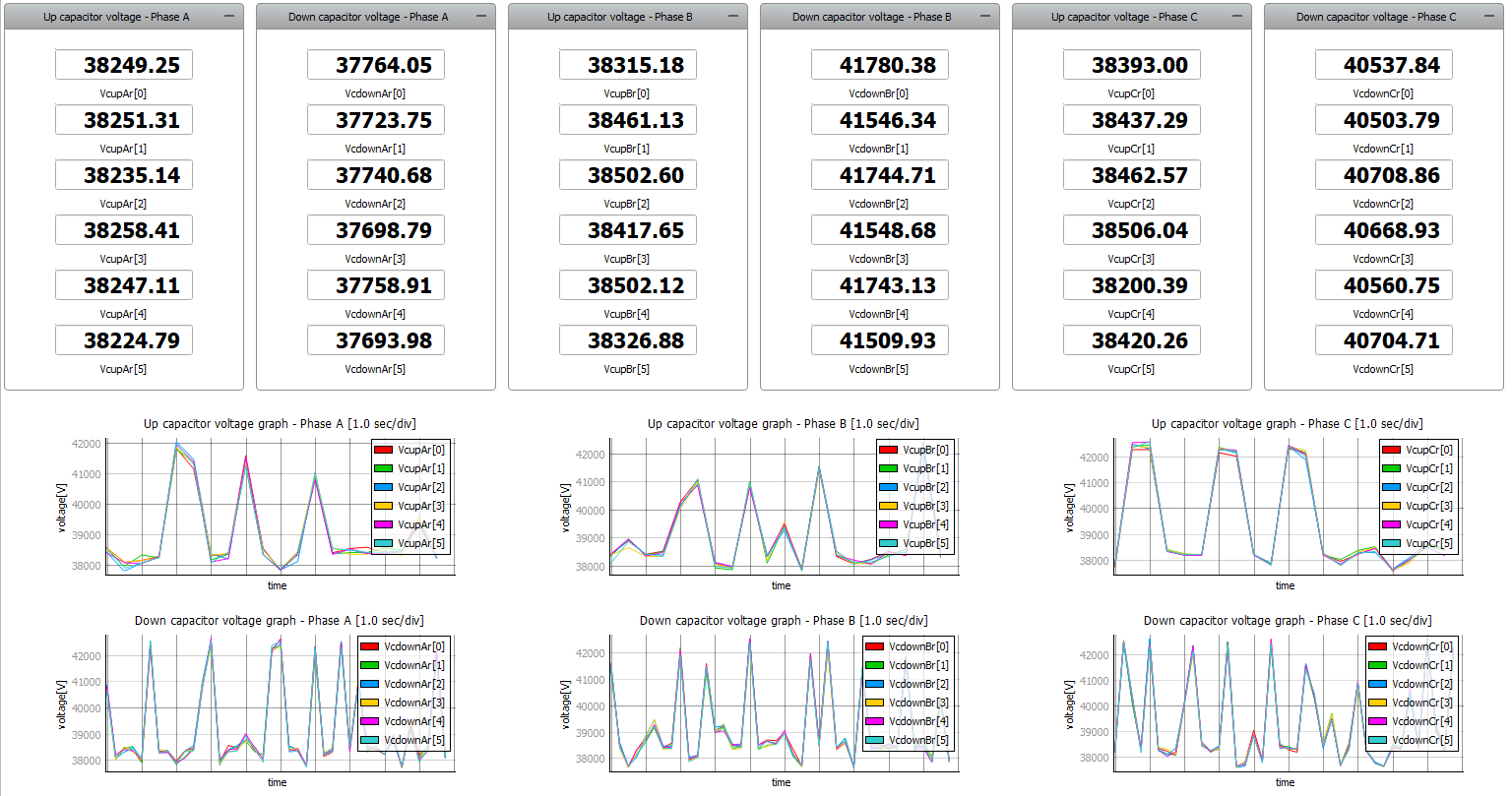

SCADA パネルでは、さまざまなウィジェットとスコープを通じてこれらのコンバーターの動作を詳細に把握できます。整流器側では、適切なスライダーを使用して DC リンクの電圧を観察および変更し、整流器側の相 A (ここではグリッド 1) の相電圧と電流の RMS 値を観察できます。MMC - 整流器サブパネルをダブルクリックすると、最初の 5 つのサブモジュールのコンデンサ間の電圧 (上アームと下アームの両方) を 3 つの相すべてについて観察できます。それらの値は、デジタル表示ウィジェットを使用して提供され、トレース グラフを使用してグラフィカルに表示されます。図 8に、MMC - 整流器サブパネルを示します。

インバータ側では、DC リンクの電圧を観測し、A 相の相電圧と電流の RMS 値を観測できます。SCADAパネルの左側にある適切なスライダーを使用して、ここではグリッド 2 と呼ばれるインバータ側の相電圧と周波数を変更できます。MMC - インバータ側サブパネルには、MMC - 整流器側サブパネルと同じように関連情報が表示されます。

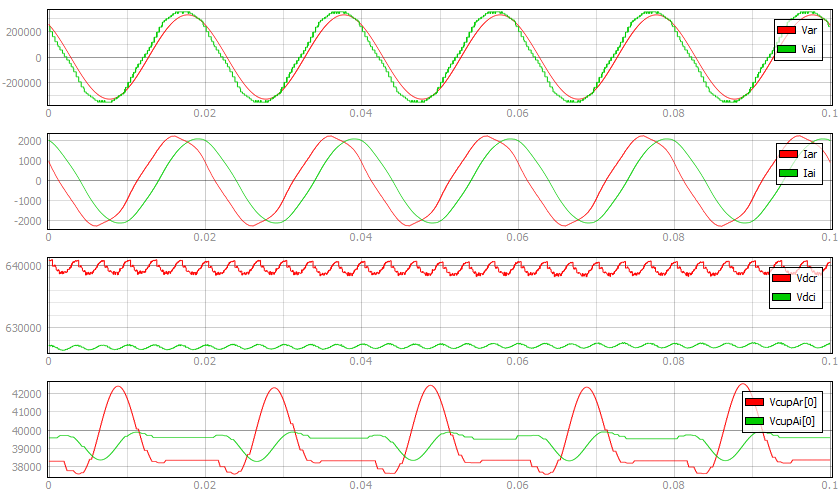

SCADAパネルには、キャプチャ/スコープウィジェットも含まれています。キャプチャでは、整流器側とインバータ側の両方の相電圧と電流を確認できます。3番目のビューポートには、整流器側とインバータ側の両方から測定されたDCリンクの電圧が表示されます。4番目のビューポートには、最初のコンデンサ両端の電圧と、コントローラが両側のコンデンサ間でこれらの電圧をどのようにバランスさせるかが表示されます。これは図9に示されています。

テスト自動化

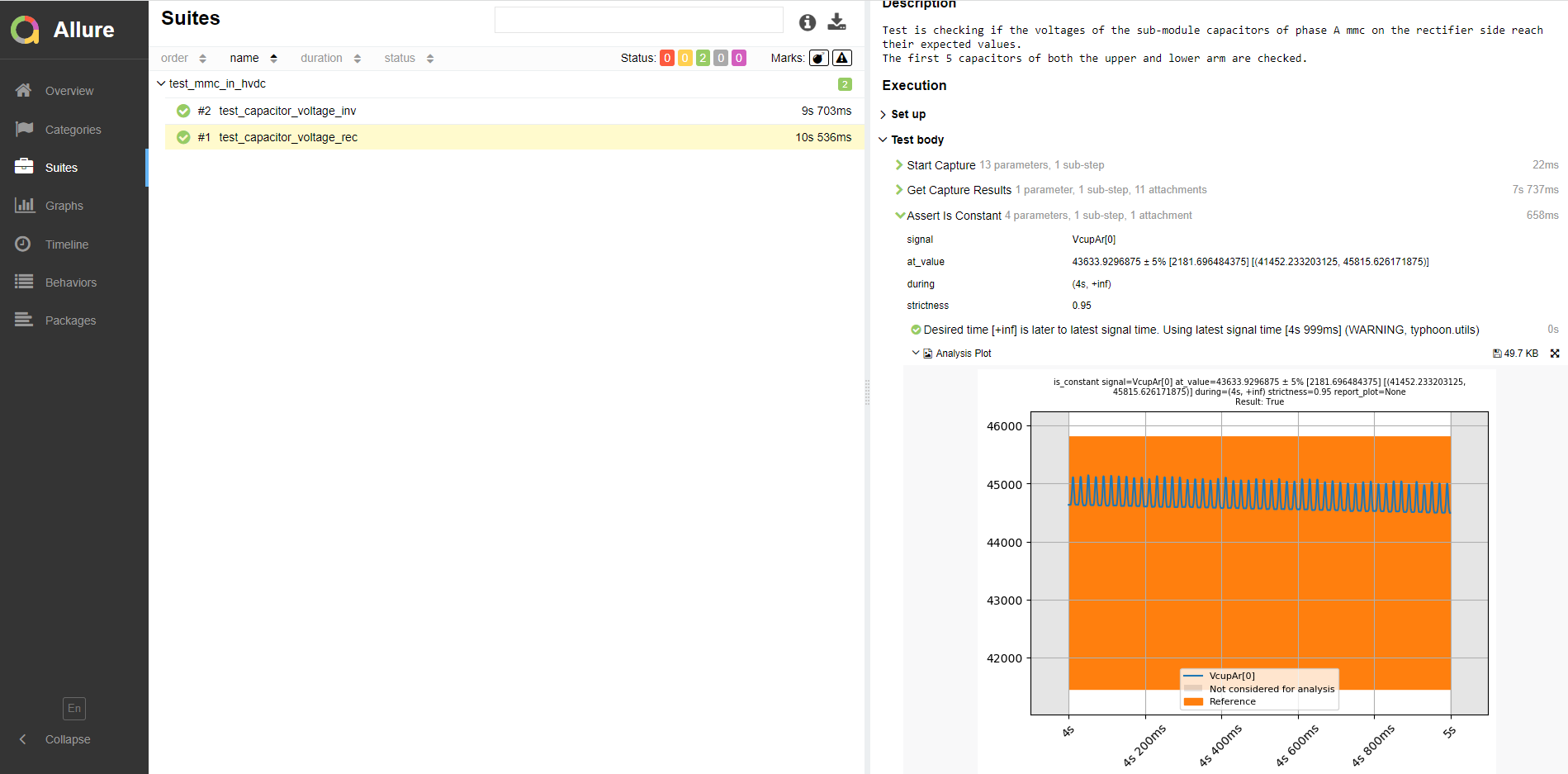

提供されているテスト自動化スクリプトは、サブモジュールの最初の10個のコンデンサのそれぞれの電圧が予想される許容範囲内にあるかどうかを検証します。テストは2つ実行され、1つは整流器側、もう1つはインバータ側です。テストはシミュレーションの最初の5秒間をキャプチャします。サブモジュールのコンデンサの電圧が安定状態にあるとき、テストはこれらの値を測定し、予想値と比較します。 この値は約44kVです。許容誤差は5%で、約2200Vです。 図10にテスト結果の例を示します。

要件の例

表1は、モデルをリアルタイムで実行するためのファイルの場所とハードウェア要件に関する詳細情報と、この最小限のハードウェア構成でモデルを実行した場合のHILデバイスのリソース使用率を示しています。この情報は、モデルの実行とカスタマイズを必要に応じて行う際に役立ちます。

| ファイル | |

|---|---|

| Typhoon HILファイル | 例\モデル\グリッド接続コンバータ\hvdcのmmc\ hvdc.tse の mmc hvdc.cus の mmc 例\テスト\111_mmc_in_hvdc\ test_mmc_in_hvdc.py |

| 最小ハードウェア要件 | |

| HILデバイス数 | 1 |

| HILデバイスモデル | HIL101 |

| デバイス構成 | 1 |

| HILデバイスのリソース利用 | |

| 処理コア数 | 1 |

| 最大マトリックスメモリ使用率 | 2.86% (コア0) |

| 最大時間枠利用率 | 63.64% (コア0) |

| シミュレーションステップ、電気 | 1マイクロ秒 |

| 実行率、信号処理 | 80マイクロ秒 |

著者

[1] ニコラ・ルチッチ

[2] シミサ・シミッチ