パラレルコンバータDTV検出器

回路図エディタにおける並列コンバータDTV検出器コンポーネントの説明

説明

並列DTV検出コンポーネントは、並列接続された2台以上のコンバータ間のシュートスルー状態を検出する、同名の専用ハードウェアユニットを構成します。このハードウェアユニットは、単一コンバータのDTVロジックとは独立して同時に動作し、並列DTV状態はHIL SCADAとHIL APIの両方で利用可能な標準DTVフラグを使用して報告されます。

コンバータを並列で扱う場合、特定のレッグに破壊的なスイッチング状態がない場合でも、並列コンバータのレッグの間でシュートスルー状態が発生する可能性があります。

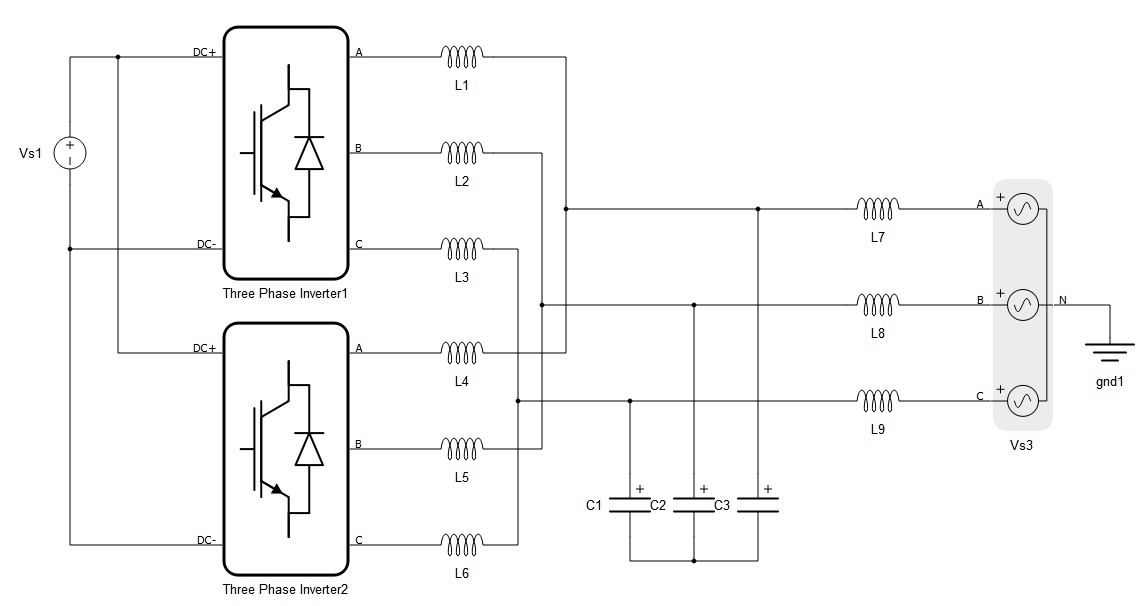

これを説明するために、図2に示すインターリーブ型系統接続コンバータを考えてみましょう。このコンバータは、2つの2レベル三相インバータを並列に接続したものです。この場合、合計12個のスイッチが6つのレグに配置され、各相に2つのレグが並列接続されています。このトポロジーの例は、図3でより詳細に示されています。

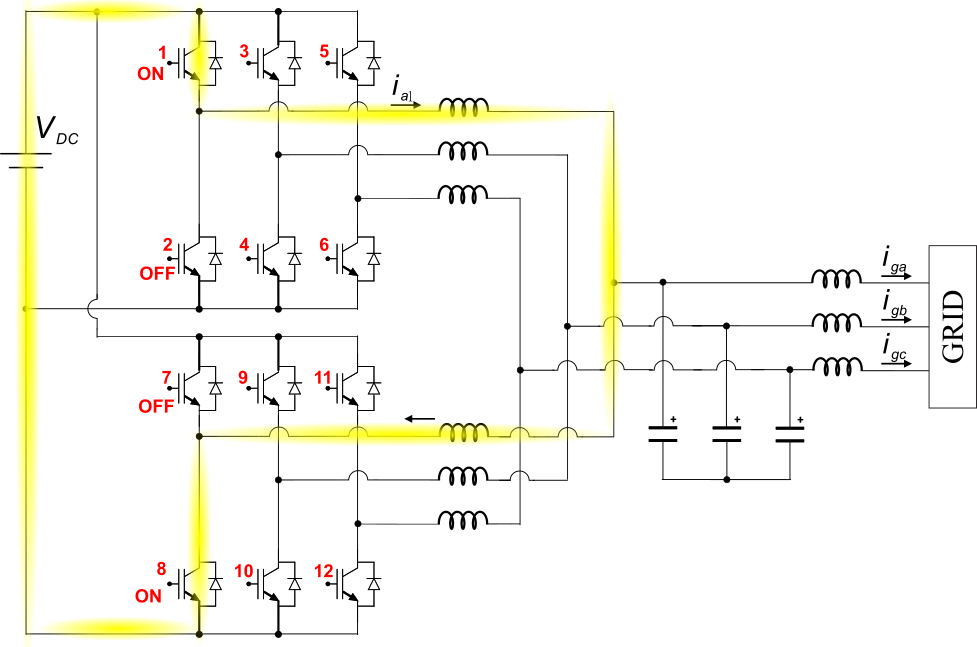

すべてのレッグが相補的なスイッチング状態で動作している場合でも、コンバータ間の並列接続によって貫通電流状態が発生する可能性があることに注意してください。例えば、図3は、スイッチ1と8を同時にオンにすることで、電源全体に低インピーダンスのパスが形成される場合を示しています。

このような望ましくない状態を検出するには、標準の DTV 検出器と同じトポロジをサポートする Parallel Converter DTV 検出器コンポーネントを使用できます。

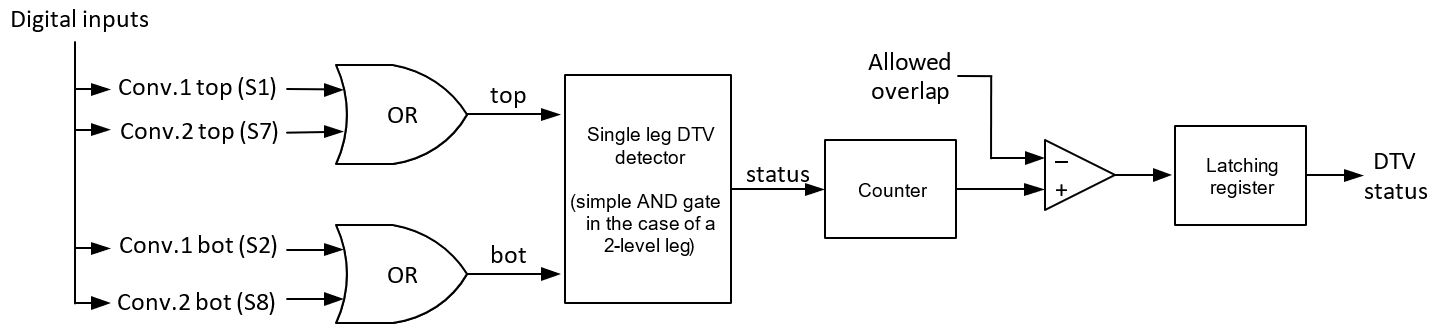

並列コンバータDTV検出コンポーネントは、機能的には単一コンバータDTV検出機能に基づいています。上に示したインターリーブコンバータの場合、図4は、A相に接続された並列レッグを考慮したコンポーネントの簡略化されたブロック図を示しています。

パラレルDTV検出コンポーネントには、コンバータレッグ間のオーバーラップ期間(許容オーバーラップ)を許容するオプションも用意されています。オーバーラップ期間検出ロジックはデジタル入力分解能に基づいて動作し、サポートされる最大オーバーラップは5μsです。

並列DTV検出器コンポーネントは現在、Typhoon HIL604およびHIL606デバイスでサポートされています。各コンポーネントは最大4つの並列レッグに対応し、デバイスごとに最大3つのコンポーネントを使用できます。つまり、デバイスごとに4つの並列3相コンバータがサポートされます。マルチHIL操作もサポートされています。

コンポーネントダイアログボックスとパラメータ

パラレル コンバータ DTV 検出器コンポーネント ダイアログ ボックスは 2 つのタブで構成されています。

タブ:「一般」

このタブでは、並列コンバータDTV検出器コンポーネントの構成を定義できます。例えば、図2に示すトポロジの場合、構成は図5に示されています。

パラレルコンバータDTV検出器「一般」パラメータ

| パラメータ | コードネーム | 説明 |

|---|---|---|

| HILデバイスID | hil_device_id | 複数のデバイスをセットアップする場合の DTV 検出ブロックの位置を定義します。 |

| 平行脚の数 | 脚番号 | 並列コンバーター レッグ数は最大 4 個までサポートされます。 |

| 脚のタイプ | 脚のタイプ | 脚タイプセレクター。 |

| ゲート入力ロジック | ゲート入力ロジック | すべての入力に共通のゲート入力ロジック。 |

| 許容重複期間 | 許容される重複 | レッグ間の許容オーバーラップ期間(秒単位)。分解能は、HIL402、602+、604デバイスでは最大6.25ns、HIL101デバイスでは最大4.5ns、HIL404、HIL506、HIL606デバイスでは最大3.5nsです。 |

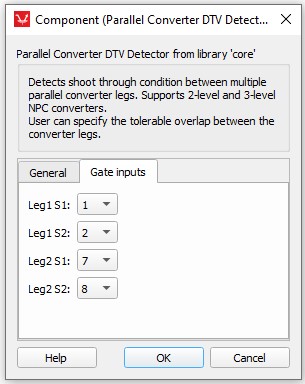

タブ:「ゲート入力」

このタブでは、並列コンバータDTV検出器コンポーネントにデジタル入力を割り当てることができます。入力数は、「並列レッグ数」と「レッグタイプ」パラメータによって異なります。図2に示すトポロジでは、各相に1つずつ、計3つの検出器コンポーネントを使用できます。A相に接続されたレッグに対する検出器コンポーネントの構成を図6に示します。B相とC相、およびそれぞれの検出器コンポーネントについても同様です。