単相3巻線変圧器

回路図エディタにおける単相3巻線変圧器コンポーネントの説明

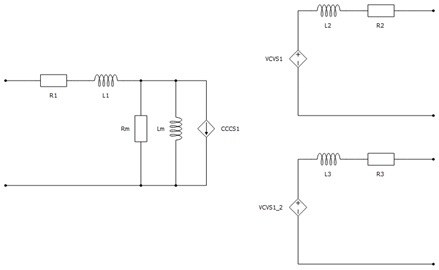

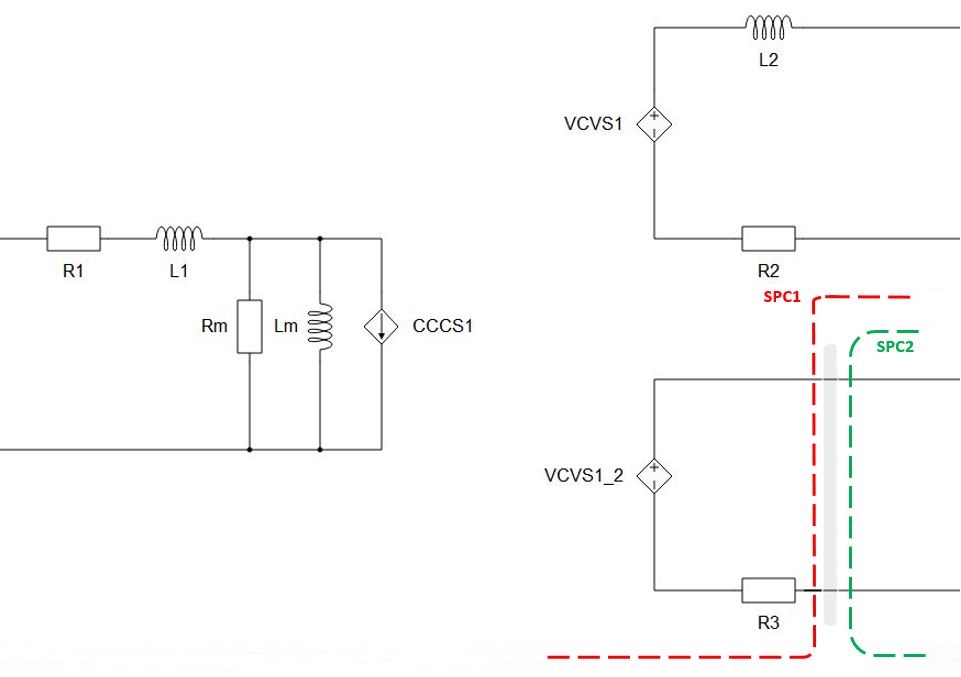

単相3巻線変圧器コンポーネントは、同一のコア上に結合された3つの巻線をモデル化します。磁化インダクタンスLmは線形または飽和特性を持ち、変圧器の一次側でモデル化されます。コア損失は、変圧器の一次側に位置するRm抵抗としてモデル化されます。また、 「コアモデル」プロパティで「Lm/Rmを無視」を選択することにより、 LmとRmを無視することも可能です。さらに、より低速なダイナミクスではヒステリシスもシミュレートできます。詳細については、 「コアモデル」セクションを参照してください。

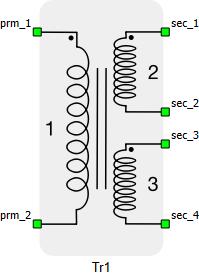

単相3巻線変圧器ブロックの概略ブロック図と対応する部品の配置および命名を図2に示します。

埋め込みカップリング

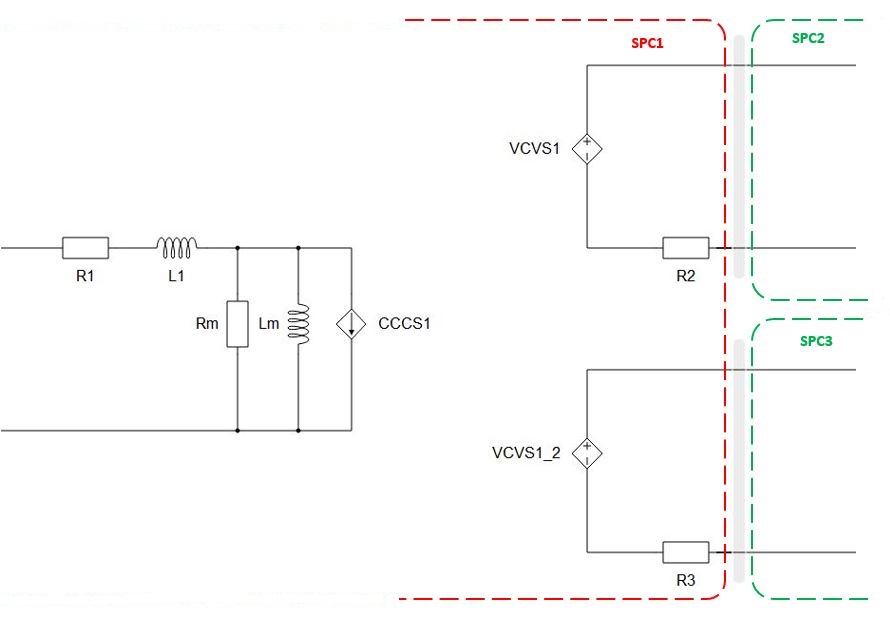

単相3巻線変圧器の埋め込み結合には、理想変圧器ベースの結合とTLM結合の2つのオプションがあります。また、巻線1と2の間、巻線1と3の間、または巻線1と3の両方に埋め込み結合を挿入することも可能です。

理想的な変圧器 埋め込みカップリング タイプは TyphoonSim では無視され、TyphoonSim シミュレーションにはまったく影響しません。

- TLM埋め込み結合タイプは、TyphoonSim 内の対応するインダクタに置き換えられます。

埋め込み結合が理想トランスフォーマーに設定されている場合、理想トランスフォーマーベースの結合がトランスフォーマーの 2 つの巻線間に配置されます。

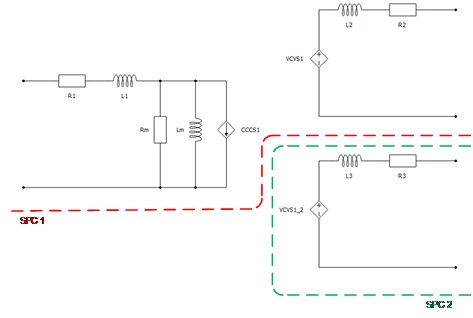

標準的な処理コア間の回路分割の視覚的な表現は次のとおりです。

Embedded coupling をTLMに設定すると、二次巻線インダクタが TLM カップリングコンポーネントに置き換えられます。インダクタンスはカップリングインダクタと組み込みインダクタに分割されます(インダクタは TLM では非表示になります)。TLM と組み込みインダクタの比率はコンパイラによって決定されますが、明示的に指定することもできます。Automatic オプションを選択した場合、比率は離散化手法によって決定されます。Manualオプションを選択した場合、ユーザー要件に合わせて比率を明示的に設定できます。TLM カップリングの詳細については、 「 Core couplings - TLM 」を参照してください。

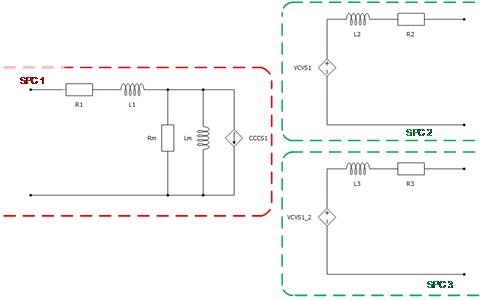

標準的な処理コア間の回路分割の視覚的な表現は次のとおりです。

ヒステリシス効果

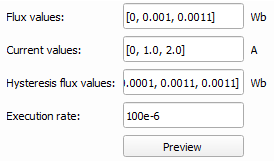

ヒステリシス効果をシミュレートするには、信号処理の実装が必要です。そのため、ヒステリシスシミュレーションの実行速度を指定する必要があります。任意の動的信号に対してこの効果を捉えるには、その周期は、ヒステリシスサンプリングの実行速度(定義: 実行率ヒステリシスは、図に示すように、変圧器または非線形インダクタの種類に応じて異なるラベルを持つ3つのリスト/配列によってさらに定義されます。 図7.

ヒステリシスを適切に定義するには、ゼロ電流データ ポイントに対してFlux 値とHysteresis flux 値の両方のデータ値を指定する必要があります。つまり、 Current 値とFlux 値のリスト/配列の最初の値は 0 で、 Hysteresis flux 値のリスト/配列の最初の値は残留フラックス値である必要があります。次に、これら 3 つのプロパティはすべて同じ数の要素を持ち、3 つすべてが単調に非減少のリスト/配列である必要があります。 Hysteresis flux 値には、 Flux 値リスト内の対応する要素よりも値が高い要素が少なくとも 1 つあり、その後に Flux 値内の対応する要素と同じ値を持つ要素が少なくとも 1 つ続く必要があります。 Hysteresis flux 値とFlux 値の最初の共通要素は、 Hysteresis upper curve thresholdとして定義されます。

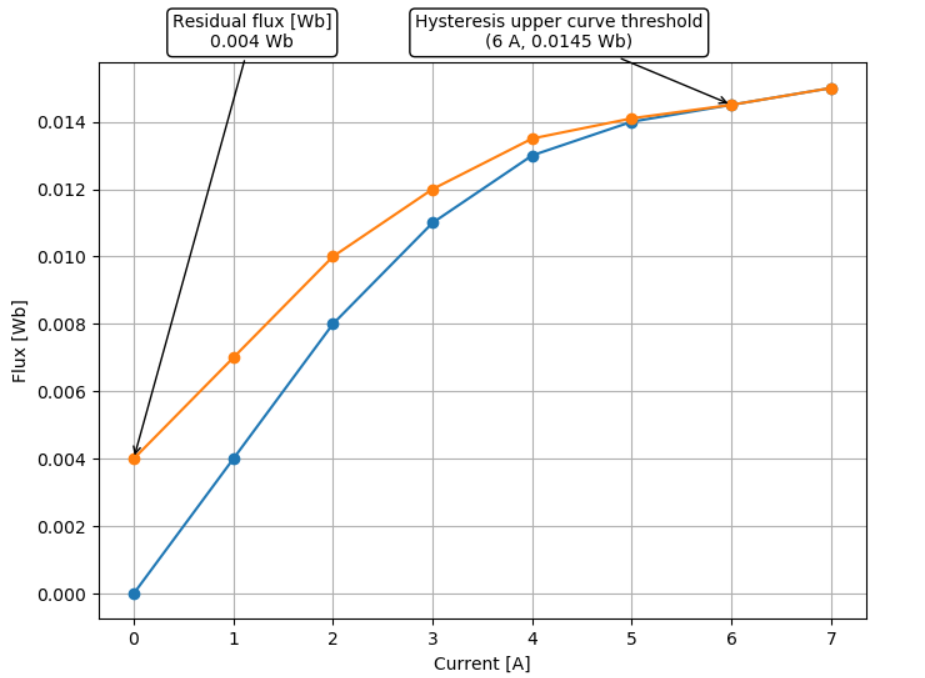

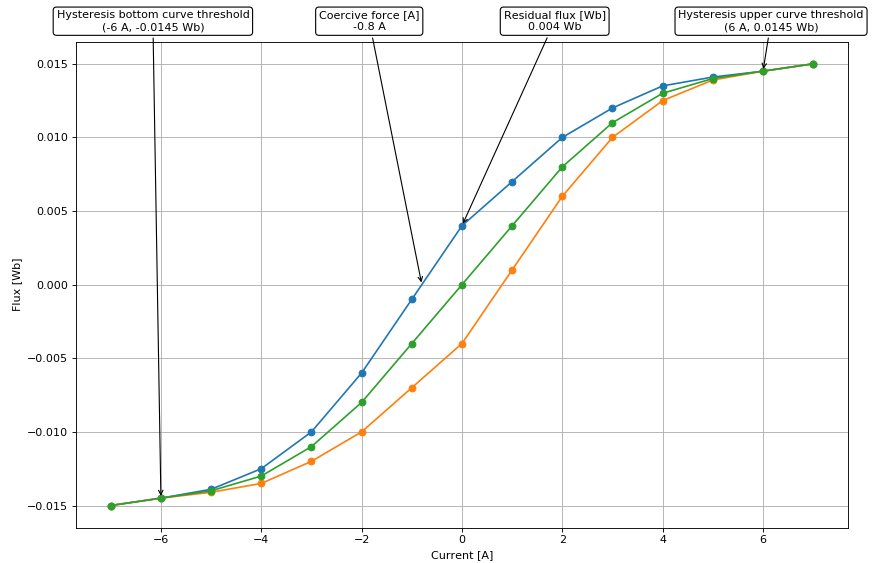

図 8 は、以下の設定を使用して適切に定義されたパラメータ値の例を示しています。

磁束値 [Wb]: [0, 0.004, 0.008, 0.011, 0.013, 0.014, 0.0145, 0.015] 電流値 [A]: [0, 1, 2, 3, 4, 5, 6, 7] ヒステリシス磁束値 [Wb]: [0.004, 0.007, 0.01, 0.012, 0.0135, 0.0141, 0.0145, 0.015]

「プレビュー」ボタンをクリックすると、ヒステリシスパラメータが検証されます。ただし、各プロパティフィールドで直接定義されている場合のみ検証され、名前空間を介して定義されている場合は検証されません。検証後、ヒステリシス曲線が延長され、図9に示すように、期待されるシミュレーションヒステリシス曲線が表示されます。

シミュレートされた磁束値がヒステリシス上限曲線しきい値を超えると、上側の曲線が磁束電流設定点の軌跡となり、次のトリガー イベントまでその状態が維持されます。シミュレートされた磁束値がヒステリシス下限曲線しきい値を下回ると、下側の曲線が磁束電流設定点の軌跡となり、次のトリガー イベントまでその状態が維持されます。シミュレーションが最初に開始されると、次のトリガー イベントまで元の曲線が基準となります。実行時にヒステリシスを無効にして基準曲線を元の磁化曲線に戻すには、scada 入力demagnetize_scada_inを1に設定します。ヒステリシス上限曲線とヒステリシス下限曲線を再度有効にするには、scada 入力demagnetize_scada_in を0に設定します。基準曲線への磁束消磁は、TyphoonSim ではまだサポートされていません。

ポート

- prm_1(電気)

- 一次巻線ポート1。

- prm_2(電気)

- 一次巻線ポート2。

- sec_1(電気)

- 二次巻線ポート1。

- sec_2(電気)

- 二次巻線ポート2。

- sec_3(電気)

- 二次巻線ポート3。

- sec_4(電気)

- 二次巻線ポート4。

一般(タブ)

- 入力パラメータ

- パラメータの形式 (SI または pu) を指定します。

- スン

- 入力パラメータが pu に設定されている場合に使用できます。

- 変圧器の公称電力[VA]。

- 脚注

- 入力パラメータが pu に設定されている場合に使用できます。

- 公称周波数[Hz]。

- V1

- 巻線1(一次側)の定格電圧[Vrms]。

- V2

- 巻線2の定格電圧[Vrms]。

- V3

- 巻線3の定格電圧[Vrms]。

- R1

- 入力パラメータが SI に設定されている場合に使用できます。

- 巻線1(一次側)の抵抗[Ω]。

- r1

- 入力パラメータが pu に設定されている場合に使用できます。

- 巻線1(一次側)の抵抗[pu]。

- L1

- 入力パラメータが SI に設定されている場合に使用できます。

- 巻線1(一次側)の漏れインダクタンス[H]。

- l1

- 入力パラメータが pu に設定されている場合に使用できます。

- 巻線1(一次側)の漏れインダクタンス[pu]。

- I1

- 入力パラメータが SI に設定されている場合に使用できます。

- 巻線1(一次側)の初期電流[A]。

- i1

- 入力パラメータが pu に設定されている場合に使用できます。

- 巻線1(一次側)の初期電流[pu]。

- R2

- 入力パラメータが SI に設定されている場合に使用できます。

- 巻線2の抵抗[Ω]。

- r2

- 入力パラメータが pu に設定されている場合に使用できます。

- 巻線2の抵抗[pu]。

- L2

- 入力パラメータが SI に設定されている場合に使用できます。

- 巻線2の漏れインダクタンス[H]。

- l2

- 入力パラメータが pu に設定されている場合に使用できます。

- 巻線2の漏れインダクタンス[pu]。

- I2

- 入力パラメータが SI に設定されている場合に使用できます。

- 巻線2の初期電流[A]。

- i2

- 入力パラメータが pu に設定されている場合に使用できます。

- 巻線2の初期電流[pu]。

- R3

- 入力パラメータが SI に設定されている場合に使用できます。

- 巻線抵抗3[Ω]。

- r3

- 入力パラメータが pu に設定されている場合に使用できます。

- 巻線3の抵抗[pu]。

- L3

- 入力パラメータが SI に設定されている場合に使用できます。

- 巻線3の漏れインダクタンス[H]。

- l3

- 入力パラメータが pu に設定されている場合に使用できます。

- 巻線3の漏れインダクタンス[pu]。

- I3

- 入力パラメータが SI に設定されている場合に使用できます。

- 巻線3の初期電流[A]。

- i3

- 入力パラメータが pu に設定されている場合に使用できます。

- 巻線3の初期電流[pu]。

- コアモデル

- 変圧器コアモデルの実装を選択します。

- モデルの忠実度には、線形、非線形、Rm/Lm 無視、ヒステリシスなど、いくつかのレベルがあります。

- 部屋

- 入力パラメータが SI に設定され、コア モデルが線形、非線形、またはヒステリシスに設定されている場合に使用できます。

- コア損失を表す抵抗[Ω]。

- rm

- 入力パラメータが pu に設定され、コア モデルが線形、非線形、またはヒステリシスに設定されている場合に使用できます。

- コア損失を表す抵抗[pu]。

- ルム

- 入力パラメータが SI に設定され、コア モデルが線形に設定されている場合に使用できます。

- 磁化インダクタンス[H]。

- 映画

- 入力パラメータが pu に設定され、コア モデルが線形に設定されている場合に使用できます。

- 磁化インダクタンス[pu]。

- フラックス値

- コア モデルが非線形またはヒステリシスに設定されている場合に使用できます。

- 磁束値[Wb]または[pu]のリスト。

- 現在の値

- コア モデルが非線形またはヒステリシスに設定されている場合に使用できます。

- 電流値のリスト [A] または [pu]。

- ヒステリシス磁束

- コア モデルがヒステリシスに設定されている場合に使用できます。

- ヒステリシスフラックス値 [Wb] または [pu] のリスト。

- 実行率

- ヒステリシス効果シミュレーションの実行率。

カップリング(タブ)

理想的な変圧器 埋め込みカップリング タイプは TyphoonSim では無視され、TyphoonSim シミュレーションにはまったく影響しません。

- TLM埋め込み結合タイプは、TyphoonSim 内の対応するインダクタに置き換えられます。

- 埋め込みカップリング1-2

- 埋め込み結合オプション - 巻線 1 と 2 の間に結合コンポーネントを挿入します - 理想トランス、TLM、またはなしに設定できます。

- TLM 1-2/組み込みコンポーネント比率

- 埋め込みカップリング1-2 が TLM に設定されている場合に使用できます。

- 内蔵インダクタへの結合比の計算方法(自動または手動)を定義します。巻線1と2間の結合に関連します。

- 埋め込みカップリング1-3

- 埋め込み結合オプション - 巻線 1 と 3 の間に結合コンポーネントを挿入します - 理想トランス、TLM、またはなしに設定できます。

- TLM 1-3/組み込みコンポーネント比率

- 埋め込みカップリング1-3 が TLM に設定されている場合に使用できます。

- 内蔵インダクタへの結合比の計算方法(自動または手動)を定義します。巻線1と3間の結合に関連します。

- カップリング要素の種類

- 対応する埋め込み結合が理想変圧器または TLM に設定されている場合に使用できます。

- 挿入されたカップリング要素がコア カップリングかデバイス カップリングかを定義します。

- HIL402 を除くすべての HIL デバイスでは、対応する組み込みカップリングが理想トランスフォーマーに設定されている場合にデバイス カップリングが利用できます。

- 比率

- 対応する埋め込み結合が TLM に設定され、TLM/埋め込みコンポーネント比率が手動に設定されている場合に使用できます。

- 組み込みインダクタへの結合比を指定します。