ヘリック

回路図エディタにおけるHERICコンバータコンポーネントの説明

回路図ブロック図

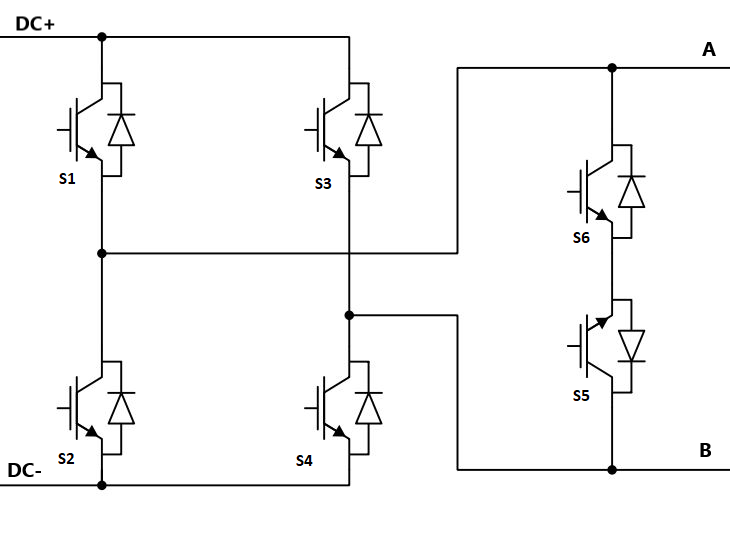

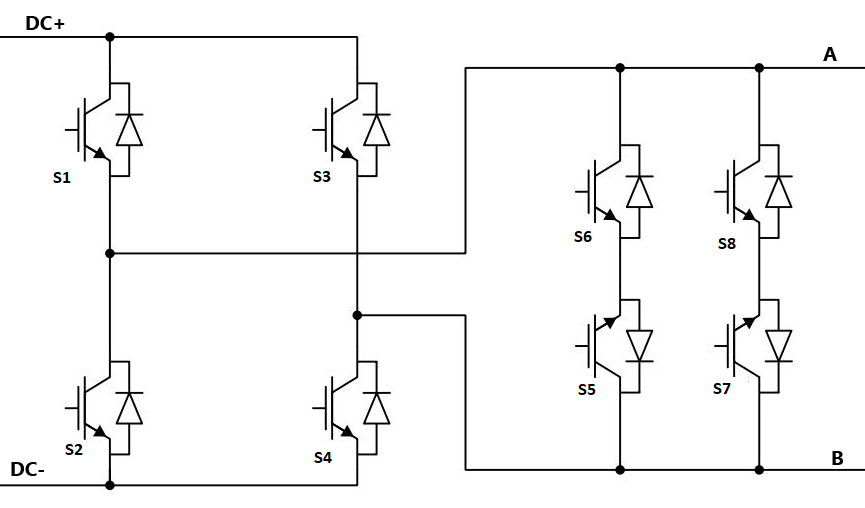

対応するスイッチの配置と名称を含むシングルACクランプHERICコンバータとダブルACクランプHERICコンバータのスイッチングブロックの概略ブロック図をそれぞれ図1と図2に示します。

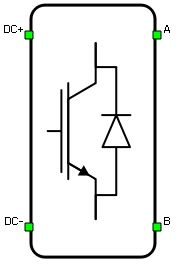

コンバータブロックのブロック図と入力パラメータを表1に示します。

| 成分 | コンポーネントダイアログウィンドウ | コンポーネントパラメータ |

|---|---|---|

HERICコンバーター |

|

|

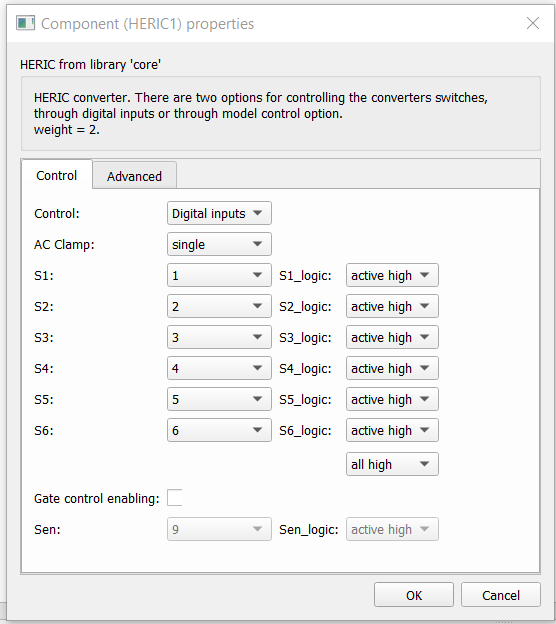

コントロール

制御パラメータとしてデジタル入力を選択すると、ゲート駆動入力を任意のデジタル入力ピン(1~32(64))に割り当てることができます。例えば、 S1に1を割り当てると、デジタル入力ピン1はS1スイッチゲート駆動ピンに配線されます。また、 gate_logicパラメータは、アクティブハイ(つまり、スイッチをオンにする高レベル入力電圧VIH)、またはアクティブロー(つまり、スイッチをオンにする低レベル入力電圧VIL)のいずれかに設定します。ゲート駆動ロジックは、外部コントローラの設計によって異なります。

モデルを制御パラメータとして選択すると、信号処理モデルから IGBT ゲート駆動信号を直接設定できます。コンポーネントに入力ピンゲートが表示され、 AC クランプタイプに応じて 6 個または 8 個のゲート駆動信号のベクトル入力が必要です。ACクランプがシングルの場合、ゲート駆動信号は次の順序である必要があります: [S1、S2、S3、S4、S5、S6]。ACクランプがダブルの場合、ゲート駆動信号は次の順序である必要があります: [S1、S2、S3、S4、S5、S6、S7、S8]。モデルから制御される場合、ロジックは常にアクティブ ハイに設定されます。

PESB最適化

PESB最適化オプションは、特定のコンバータモデルで利用可能です。PESB最適化を有効にすると、すべてのコンバータの短絡状態空間モードが統合され、同じ状態空間モードとして扱われます。例えば、三相コンバータ内の1つのレグが短絡し、PESB最適化が有効になっている場合、三相コンバータ内のすべてのレグも短絡状態になります。この短絡モデリングの簡素化により、マトリックスメモリを大幅に節約できます。

デジタルエイリアス

コンバータがデジタル入力で制御される場合、コンバータが使用するすべてのデジタル入力にエイリアスが作成されます。デジタル入力エイリアスは、既存のデジタル入力信号と並んで「デジタル入力」リストに表示されます。エイリアスは「Converter_name.Switch_name」のように表示されます。ここで、 「Converter_name」はコンバータのコンポーネント名、 「Switch_name」はコンバータ内の制御可能なスイッチ名です。