ウィーン整流器

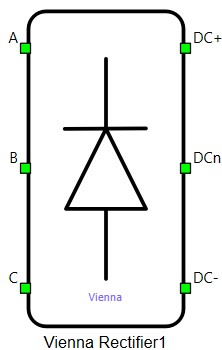

回路図エディタにおける Vienna Rectifier コンポーネントの説明

概略ブロック図

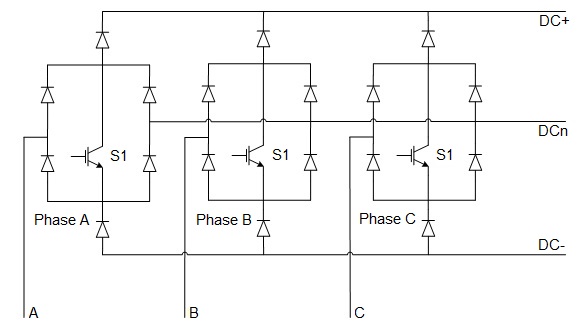

対応するスイッチの名称を含む Vienna 整流器の概略ブロック図を図 2に示します。

リアルタイム/VHIL シミュレーション用の Vienna Rectifier コンポーネントの重みは 3 です。

コントロール

制御パラメータとしてデジタル入力を選択すると、ゲート駆動入力を任意のデジタル入力ピン(1~32(64))に割り当てることができます。例えば、 S1を1に割り当てると、デジタル入力ピン1はS1スイッチゲート駆動ピンに配線されます。また、 gate_logicパラメータでは、外部コントローラの設計に応じて、アクティブハイ(高レベル入力電圧VIHでスイッチがオン)またはアクティブロー(低レベル入力電圧VILでスイッチがオン)のゲート駆動ロジックを選択します。TyphoonSimでは、デジタル信号は内部仮想IOバスから読み取られます。したがって、デジタル出力1に何らかの信号が送られると、デジタル入力1にも出力されます。

制御パラメータとして「モデル」を選択すると、信号処理モデルからスイッチのゲート駆動信号を直接設定できます。コンポーネント上に入力ピン「gates」が表示されます。これは3要素のベクトル入力で、最初の値(インデックス0)はフェーズAのS1ゲート、2番目の値(インデックス1)はフェーズBのS1ゲート、3番目の値(インデックス2)はフェーズCのS1ゲートを制御します。モデルから制御する場合、ロジックは常にアクティブハイになります。

デジタルエイリアス

コンバータがデジタル入力で制御される場合、コンバータが使用するすべてのデジタル入力にエイリアスが作成されます。デジタル入力エイリアスは、既存のデジタル入力信号と並んで「デジタル入力」リストに表示されます。エイリアスは「Converter_name.Switch_name」のように表示されます。ここで、 「Converter_name」はコンバータのコンポーネント名、 「Switch_name」はコンバータ内の制御可能なスイッチ名です。

ポート

- DC+(電気)

- DC側+ポート。

- DCn(電気)

- DC 側 n ポート。

- DC(電気)

- DC側ポート。

- A(電気)

- AC側Aポート

- B(電気)

- AC側Bポート

- C(電気)

- AC側Cポート

- ゲート(イン)

- モデル制御を選択した場合に使用可能

- スイッチ用の3つの入力ゲート信号のベクトル

一般(タブ)

- コントロール

- スイッチの制御方法を指定します。デジタル入力とモデルから選択できます。

- 各コントロールの詳細については、 「コントロール」セクションをご覧ください。

- もし デジタル入力 コントロールとして選択した場合、次のプロパティを使用できます。

- フェーズA S1

- Phase A S1スイッチを制御するために使用されるデジタル入力

- フェーズA S1ロジック

- フェーズA S1の制御信号に適用されるロジック

- アクティブハイまたはアクティブロー

- フェーズB S1

- フェーズB S1スイッチを制御するために使用されるデジタル入力

- フェーズB S1ロジック

- フェーズB S1の制御信号に適用されるロジック

- アクティブハイまたはアクティブロー

- フェーズC S1

- Phase C S1スイッチを制御するために使用されるデジタル入力

- フェーズC S1ロジック

- フェーズC S1の制御信号に適用されるロジック

- アクティブハイまたはアクティブロー

- ゲート制御の有効化

- 有効にすると、ゲート制御信号の変更を適用するかどうかを制御できるようになります。

- セン

- ゲート制御の有効化が有効になっている場合に利用可能

- スイッチングを有効/無効にするデジタル入力

- Sen_logic

- ゲート制御の有効化が有効になっている場合に利用可能

- Sen信号に適用されるロジック

- フェーズA S1

- もし モデル コントロールとして選択した場合、次のプロパティを使用できます。

- 実行率

- コンポーネントのゲート信号の更新間隔を定義します。ゲート信号は、コンポーネントへの信号処理入力として提供されます。

- 実行率

特典(タブ)

- パブリック - パブリックとしてマークされたコンポーネントは、すべてのレベルでシグナルを公開します。

- 保護済み - 保護済みとしてマークされたコンポーネントは、最初のロックされた親コンポーネントの外部のコンポーネントへの信号を非表示にします。

- 継承 - 継承としてマークされたコンポーネントは、継承以外の値に設定されている最も近い親の 'signal_access' プロパティ値を取得します。