2ダイオード全波整流器

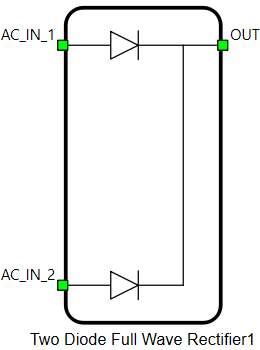

回路図エディタにおける2つのダイオード全波整流器コンポーネントの説明

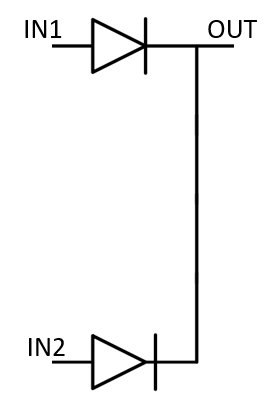

概略ブロック図

2ダイオード全波整流器の概略ブロック図を図2に示します。

リアルタイム/VHIL シミュレーション用の 2 つのダイオード全波整流器コンポーネントの重みは 1 です。

ポート

- AC_IN_1(電気)

- AC側IN1ポート。

- AC_IN_2(電気)

- AC側IN2ポート。

- 出力(電気)

- DC側ポート

一般(タブ)

- 逆ダイオード方向

- 逆ダイオード方向を有効にする

特典(タブ)

「エクストラ」タブでは、 信号アクセス管理 コンポーネント用。

シグナルの可視性は、「signal_access」プロパティと、その階層内の親コンポーネントがロックされているかどうかに基づいて計算されます。ロックされたコンポーネントに含まれていないコンポーネントは、「signal_access」プロパティに関係なくシグナルを公開します。「signal_access」プロパティは、以下の3つの値のいずれかになります。

- パブリック - パブリックとしてマークされたコンポーネントは、すべてのレベルでシグナルを公開します。

- 保護済み - 保護済みとしてマークされたコンポーネントは、最初のロックされた親コンポーネントの外部のコンポーネントへの信号を非表示にします。

- 継承 - 継承としてマークされたコンポーネントは、継承以外の値に設定されている最も近い親の 'signal_access' プロパティ値を取得します。

注:リアルタイムシミュレーションでは、両方のダイオードが導通しているケースはこのモデルではサポートされていません。両方のダイオードに順方向バイアスがかかっている場合は、片方のダイオードだけが導通します。