共振コンバータ

回路図エディタの共振コンバータ コンポーネントの説明。

回路図ブロック図

共振コンバータ コンポーネントは、CLLLC 共振コンバータと LLC 共振コンバータの 2 つの主要なトポロジをサポートします。

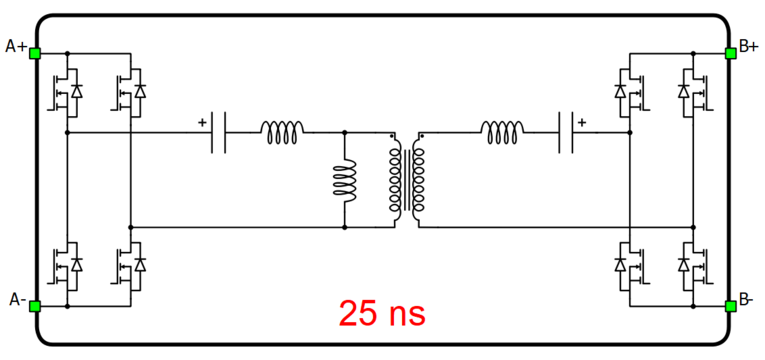

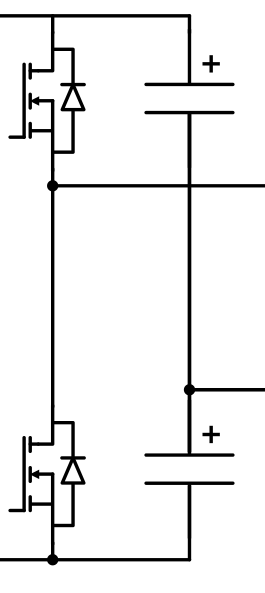

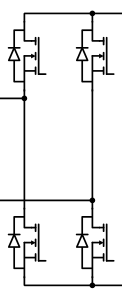

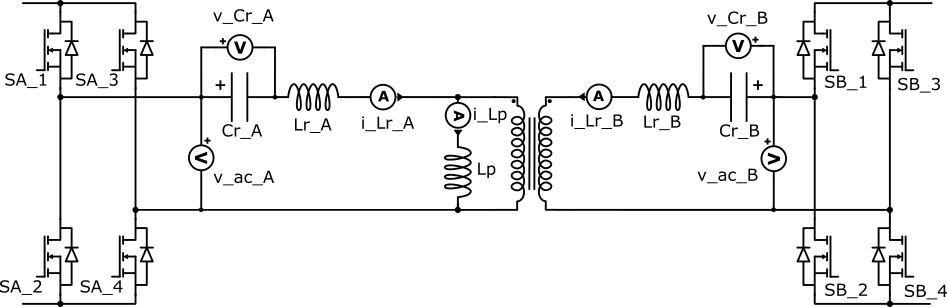

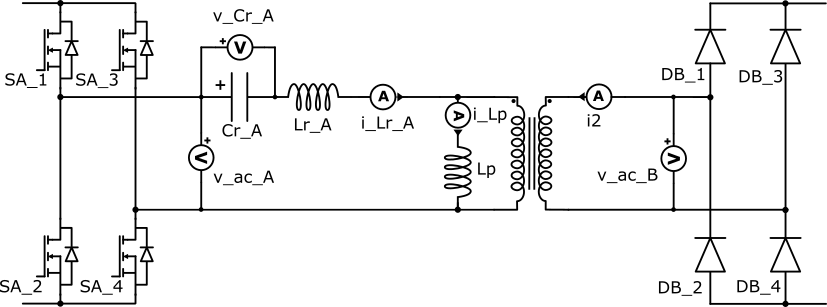

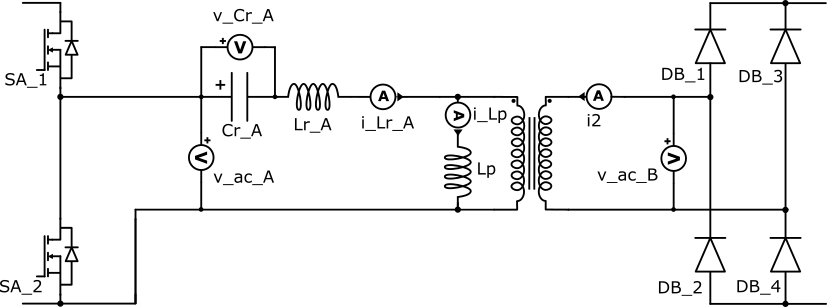

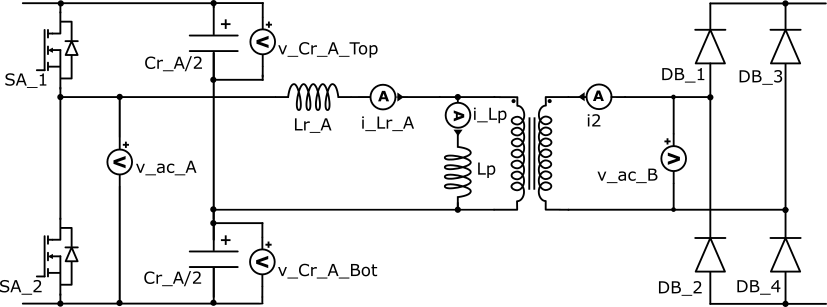

CLLLC 共振コンバータの概略ブロック図と対応するスイッチの名称を図 2に示します。

リアルタイム シミュレーションでは、このコンバータ ブロックは専用のDC-DC コンバータ ソルバーFPGA ハードウェア リソースを使用して、このトポロジのシミュレーション ステップを削減します。

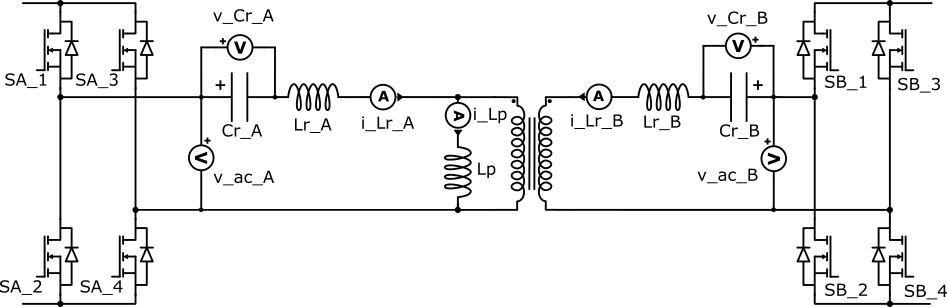

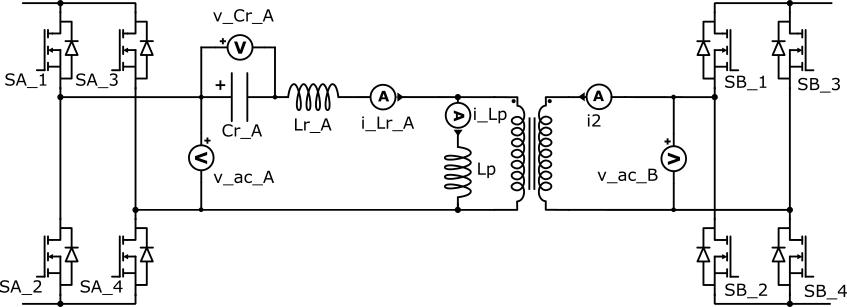

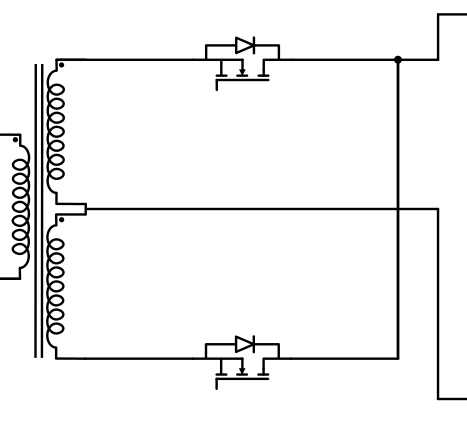

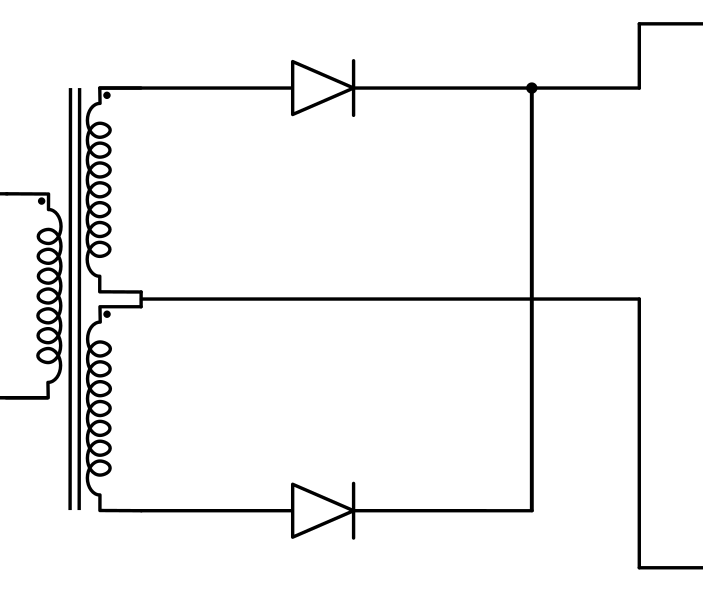

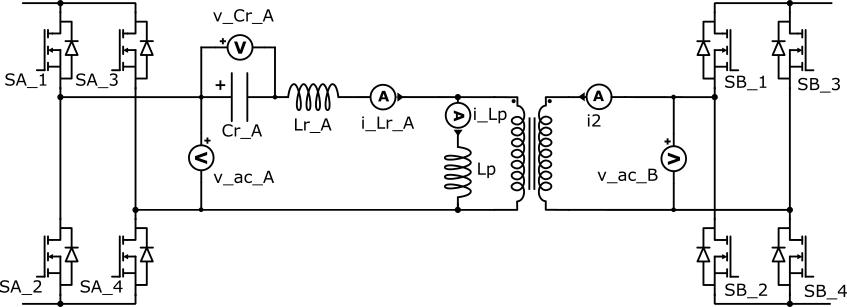

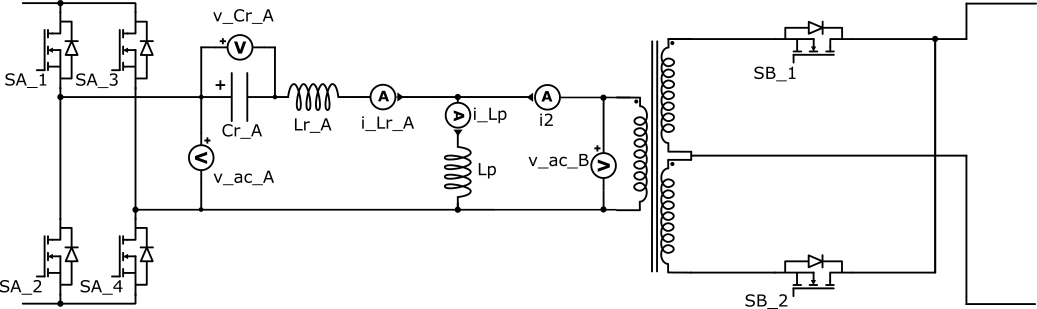

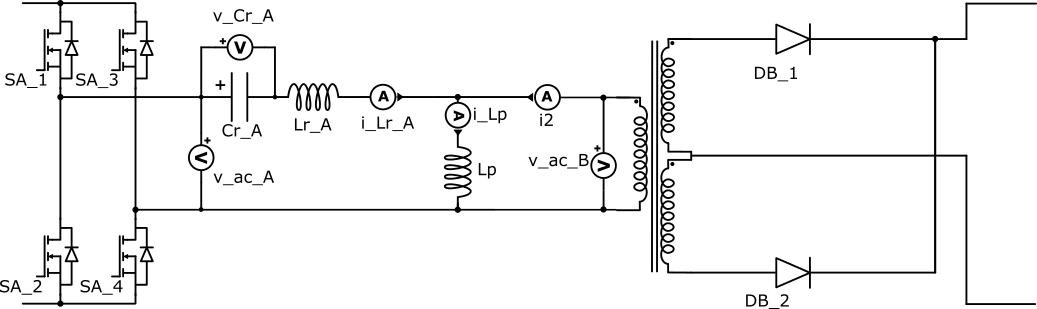

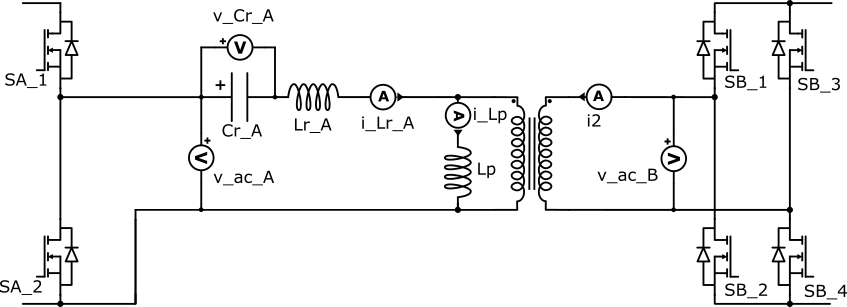

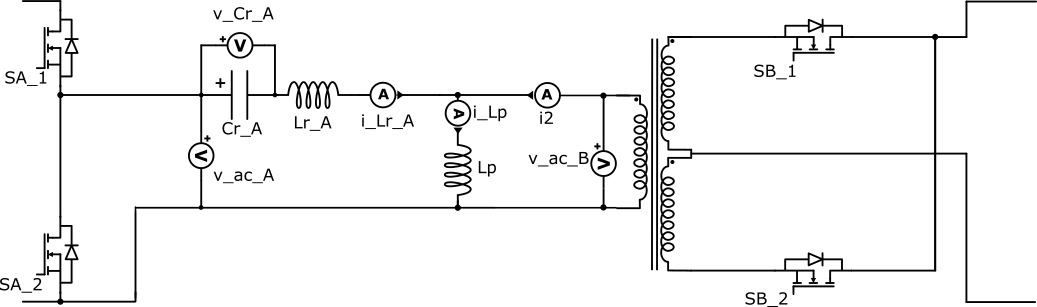

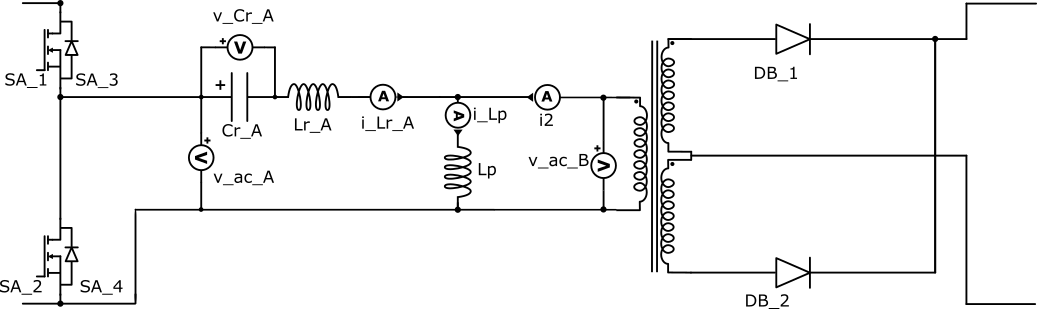

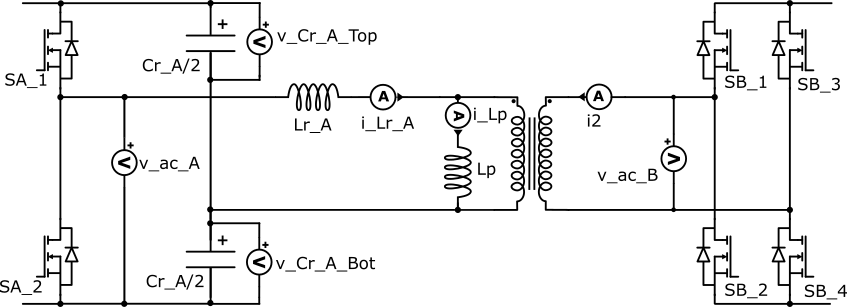

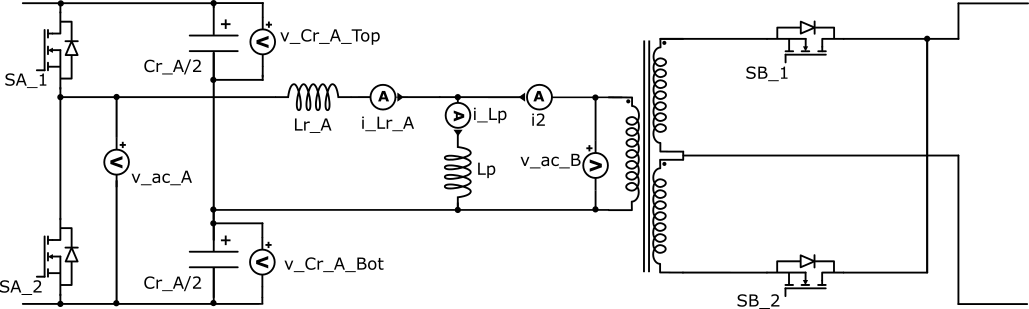

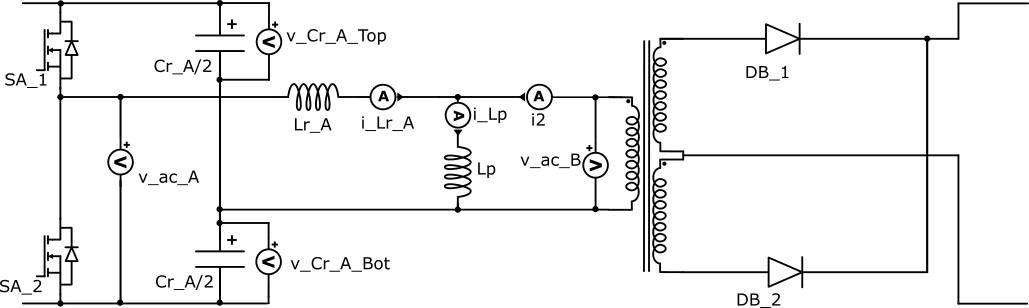

LLC共振コンバータの概略ブロック図と対応するスイッチの名称を図3に示します。

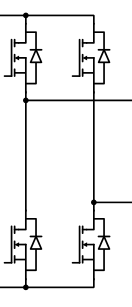

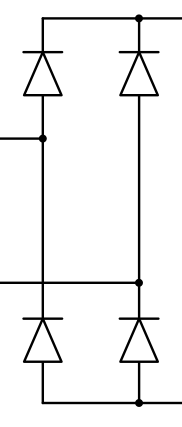

共振タンクとしてLLCを選択した場合、A側とB側の異なるトポロジを選択できます。表1はA側トポロジの概要を示し、表2はB側トポロジの概要を示します。

| 名前 | トポロジー |

|---|---|

|

Hブリッジ |

|

|

ハーフブリッジ |

|

|

ハーフブリッジスプリットキャップ |

|

| 名前 | トポロジー |

|---|---|

|

Hブリッジ |

|

|

フルブリッジ整流器 |

|

|

アクティブセンタータップ |

|

|

ダイオードセンタータップ |

|

コントロール

制御パラメータとしてデジタル入力を選択すると、ゲート駆動入力を任意のデジタル入力ピン(1~32(64))に割り当てることができます。たとえば、 SA_1に1を割り当てると、デジタル入力ピン1はSA_1スイッチゲート駆動ピンに配線されます。また、 gate_logicパラメータでは、外部コントローラの設計に応じて、アクティブハイ(高レベル入力電圧VIHでスイッチがオン)またはアクティブロー(低レベル入力電圧VILでスイッチがオン)のゲート駆動ロジックを選択します。TyphoonSimでは、デジタル信号は内部仮想IOバスから読み取られます。したがって、デジタル出力1に何らかの信号が送られると、デジタル入力1にも出力されます。

制御パラメータとして内部変調器を選択すると、デジタル入力ピンの代わりにスイッチを駆動するための内部 PWM 変調器の使用が有効になります。

- CLLLC 共振コンバータの場合、この構成では 10 個の追加コンポーネント入力が存在します。En_A およびEn_B入力は、対応する側でスイッチングを有効/無効にするために使用されます。In_a1 、 In_a2 、 In_b1 、およびIn_b2 は、それぞれレッグA1 、 A2 、 B1 、およびB2 の対応する内部 PWM 変調器の参照信号入力として使用されます。さらに、 Offset_a1 、 Offset_a2 、 Offset_b1 、およびOffset_b2は、それぞれレッグA1 、 A2 、 B1 、およびB2の対応する内部 PWM 変調器のキャリア オフセットとして使用されます。共振コンバータの内部変調器の動作モードとして可変搬送周波数を選択した場合は、追加のポートFreqが存在します。このポートは、内部 PWM 変調器の周波数入力として使用されます。

- LLC 共振コンバーターの場合、この構成では、内部変調器は A 側のスイッチのみを駆動し、B 側の制御可能なスイッチ (選択された B トポロジーに存在する場合) はオフになるため、B 側は完全にパッシブとして動作します。 この構成では、5 つの追加コンポーネント入力が存在します。 En入力は、スイッチングを有効/無効にするのに使用されます。 In_a1とIn_a2 は、それぞれレッグA1とA2の対応する内部 PWM 変調器の参照信号入力として使用されます。 また、 Offset_a1とOffset_a2 は、それぞれレッグA1とA2 の対応する内部 PWM 変調器のキャリア オフセットとして使用されます。 A 側トポロジーがH ブリッジでない場合、 In_a2とOffset_a2 は存在しません。 共振コンバーターの内部変調器の動作モードとして可変搬送周波数を選択した場合、追加のポートFreq が存在します。

特典

リアルタイムシミュレーションでは、 「短絡抵抗 - A」と「短絡抵抗 - B」は、一部のレグが短絡モードになった場合に考慮される抵抗を定義するために使用されます。短絡は短絡抵抗を使用してモデル化されます。つまり、レグが短絡モードになった場合、対応するDC側から引き出される電流はVdc_A(B)/短絡抵抗 - A(B)となります。ここで、 Vdc_A(B)は対応するDC側のDC電圧です。

リアルタイムシミュレーションにおけるモデル記述

リアルタイムシミュレーションでは、共振コンバータはDC-DCコンバータソルバー専用ハードウェアソルバーモジュール上で実行されます。このソルバーは、高速スイッチングコンバータトポロジのダイナミクスを高解像度でシミュレートするために高度に最適化されています。つまり、共振コンバータブロックは、他のコンバータブロックで通常使用されるリソースを使用しないため、共振コンバータの重みは0です。

リアルタイムシミュレーションにおける電気回路インターフェース

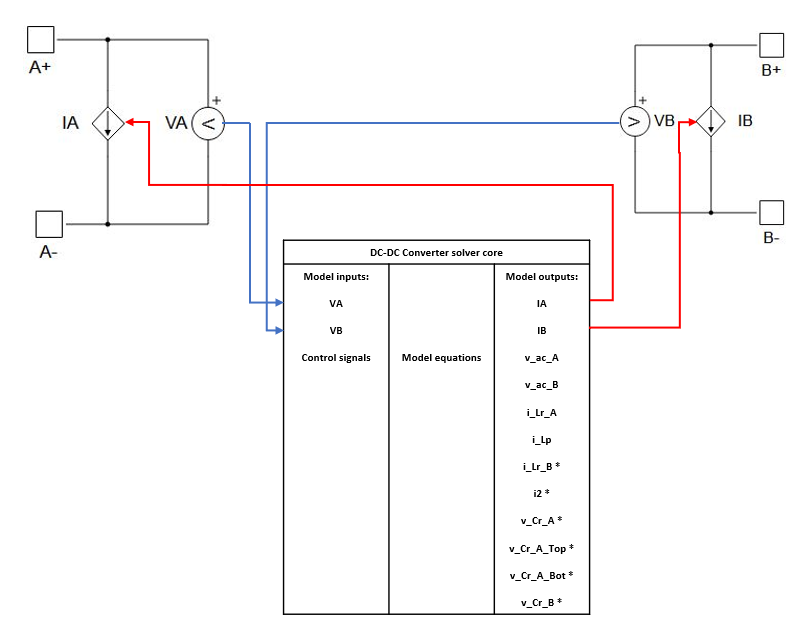

リアルタイムシミュレーションでは、 「電気回路インターフェース」で説明されているように、 DC-DCコンバータソルバーハードウェアリソースを使用するすべてのコンポーネントには、回路の他の部分とインターフェースする電気回路が含まれています。Typhoon HIL回路図エディタライブラリの共振コンバータコンポーネントは、電流源インターフェースを使用します。このインターフェースは、電圧が専用のDC-DCコンバータソルバーコアへの入力となり、電流が専用のDC-DCコンバータソルバーコアからの出力となるように定式化されています。図4は、共振コンバータコンポーネントの回路インターフェースを示しています。

周囲の回路に直接影響を与えるIAとIBに加えて、内部の電気測定結果を表すコンポーネント出力も存在します。表3は、トポロジに応じて利用可能な測定結果を示しています。末尾に「.cmp_out」が付く信号は、大なり小なり演算子を用いてアナログ信号をゼロと比較するデジタルコンパレータ信号であり、ソルバーのステップレートで更新されます。

| 共鳴タンク | サイドトポロジー | Bサイドトポロジ | 測定 |

|---|---|---|---|

|

CLLLC |

Hブリッジ |

Hブリッジ |

i_Lr_A、i_Lr_A.cmp_out、i_Lr_B、i_Lr_B.cmp_out、i_Lp、v_Cr_A、v_Cr_B、v_ac_A、v_ac_B |

|

LLC |

Hブリッジ、ハーフブリッジ |

全て |

i_Lr_A、i_Lr_A.cmp_out、i2、i2.cmp_out、i_Lp、v_Cr_A、v_ac_A、v_ac_B |

|

LLC |

ハーフブリッジスプリットキャップ |

全て |

i_Lr_A、i_Lr_A.cmp_out、i2、i2.cmp_out、i_Lp、v_Cr_A_Top、v_Cr_A_Bot、v_ac_A、v_ac_B |

すべてのトポロジのすべての測定の配置は、対応するスイッチ命名セクションを含む共振コンバータ コンポーネントのブロック図に表示されます。

対応するスイッチ名を含む共振コンバータコンポーネントのブロック図

このセクションには、LLC 共振コンバータのA 側トポロジとB 側トポロジのすべての組み合わせに対応するスイッチ名を含む共振コンバータ コンポーネントのブロック ダイアグラムと、CLLLC 共振コンバータのブロック ダイアグラムが含まれています。

デジタルエイリアス

コンバータがデジタル入力で制御される場合、コンバータが使用するすべてのデジタル入力にエイリアスが作成されます。デジタル入力エイリアスは、既存のデジタル入力信号と並んで「デジタル入力」リストに表示されます。エイリアスは「Converter_name.Switch_name」のように表示されます。ここで、 「Converter_name」はコンバータのコンポーネント名、 「Switch_name」はコンバータ内の制御可能なスイッチ名です。

ポート

- A+(電気)

- DC側A+ポート。

- A-(電気)

- DC 側 A ポート。

- B+(電気)

- DC 側 B+ ポート。

- B-(電気)

- DC側Bポート。

コントロール(タブ)

- コントロール

- スイッチの制御方法を指定します。デジタル入力と内部変調器のいずれかを選択できます。

- 各コントロールの詳細については、 「コントロール」セクションをご覧ください。

- もし デジタル入力 コントロールとして選択した場合、次のプロパティを使用できます。

- SA_1

- SA_1スイッチを制御するために使用されるデジタル入力

- SA_1_ロジック

- SA_1の制御信号に適用されるロジック

- アクティブハイまたはアクティブロー

- SA_2

- SA_2スイッチを制御するために使用されるデジタル入力

- SA_2_ロジック

- SA_2の制御信号に適用されるロジック

- アクティブハイまたはアクティブロー

- SA_3

- SA_3スイッチを制御するために使用されるデジタル入力

- SA_3_ロジック

- SA_3の制御信号に適用されるロジック

- アクティブハイまたはアクティブロー

- SA_4

- SA_4スイッチを制御するために使用されるデジタル入力

- SA_4_ロジック

- SA_4の制御信号に適用されるロジック

- アクティブハイまたはアクティブロー

- SB_1

- SB_1スイッチを制御するために使用されるデジタル入力

- SB_1_ロジック

- SB_1の制御信号に適用されるロジック

- アクティブハイまたはアクティブロー

- SB_2

- SB_2スイッチを制御するために使用されるデジタル入力

- SB_2_ロジック

- SB_2の制御信号に適用されるロジック

- アクティブハイまたはアクティブロー

- SB_3

- SB_3スイッチを制御するために使用されるデジタル入力

- SB_3_ロジック

- SB_3の制御信号に適用されるロジック

- アクティブハイまたはアクティブロー

- SB_4

- SB_4スイッチを制御するために使用されるデジタル入力

- SB_4_ロジック

- SB_4の制御信号に適用されるロジック

- アクティブハイまたはアクティブロー

- ゲート制御有効化 -A

- 有効にすると、コンバータAのゲート制御信号の変更を適用するかどうかを制御できるようになります。

- センA

- ゲート制御有効化 -A が有効な場合に使用可能

- コンバータAのスイッチングを有効/無効にするデジタル入力

- Sen_logic -A

- ゲート制御有効化 -A が有効な場合に使用可能

- Sen-A信号に適用されるロジック

- ゲート制御有効化 -B

- 有効にすると、コンバータBのゲート制御信号の変更を適用するかどうかを制御できるようになります。

- センB

- ゲート制御有効化 -B が有効な場合に使用可能

- コンバータBのスイッチングを有効/無効にするデジタル入力

- Sen_logic -B

- ゲート制御有効化 -B が有効な場合に使用可能

- Sen -B信号に適用されるロジック

- SA_1

- もし 内部変調器 コントロールとして選択した場合、次のプロパティを使用できます。

- 動作モード

- 内部変調器の搬送周波数のソースを指定します

- 動作モードが固定搬送周波数の場合、コンポーネントのプロパティで周波数を指定できます。

- 動作モードが可変搬送周波数の場合、信号処理ポートを使用して周波数を指定できます。

- 搬送周波数(Hz)

- 動作モードが固定搬送周波数の場合に使用可能

- 内部変調器の搬送周波数を指定します

- デッドタイム

- 内部変調器のデッドタイムを秒単位で指定します

- 基準信号[最小、最大]

- 搬送信号の最小値と最大値を指定します

- 最小キャリア信号値と最大キャリア信号値の2つの値を含むベクトル

- ロードモード

- 内部変調器に変調信号の新しい値が適用されるイベントを指定します。

- 最小値を選択した場合、キャリアが最小値に達したときに新しい値が適用されます。

- 最大値を選択した場合、キャリアが最大値に達したときに新しい値が適用されます。

- どちらかを選択した場合、キャリアが最小値または最大値に達したときに新しい値が適用されます。

- 内部変調器に変調信号の新しい値が適用されるイベントを指定します。

- 動作モード

電気(タブ)

- 共鳴タンク

- 共振コンバーター タンクのタイプ - LLC または CLLLC。

- サイドトポロジー

- A側のコンバータトポロジ

- CLLLCを選択した場合、Hブリッジのみが利用可能

- LLCを選択した場合、Hブリッジ、ハーフブリッジ、ハーフブリッジスプリットキャップが利用可能

- Bサイドトポロジ

- B側のコンバータトポロジ

- CLLLCを選択した場合、Hブリッジのみが利用可能

- LLCを選択した場合、Hブリッジ、フルブリッジ整流器、アクティブセンタータップ、ダイオードセンタータップが利用可能

- 直列インダクタンス(A)

- A側の直列共振インダクタンス

- 静電容量(A)

- A側の直列共振容量。ハーフブリッジ分割コンデンサトポロジを選択した場合、このプロパティはA側の両方のコンデンサの合計容量を表します。

- 並列インダクタンス

- 並列インダクタのインダクタンス

- Rシリーズ(A)

- A側の直列抵抗

- 直列インダクタンス(B)

- B側の直列共振インダクタンス

- CLLLC共振タンクを選択した場合に使用可能

- 静電容量(B)

- B 側の直列共振容量。

- CLLLC共振タンクを選択した場合に使用可能

- Rシリーズ(B)

- B側の直列抵抗

- CLLLC共振タンクを選択した場合に使用可能

- トランスの巻数比(B/A)

- B 側と A 側の間の内部変圧器比を定義します。センタータップ トポロジを選択した場合、すべての二次巻線は同じであると見なされ、B は単一巻線の巻数を表します。

特典(タブ)

- 短絡抵抗 - A

- A側が短絡した場合の短絡電流を計算するために使用されるA側の抵抗

このプロパティはTyphoonSimではサポートされていません。値を変更してもTyphoonSimのシミュレーションにはまったく影響しません。

- 短絡抵抗 - B

- B側が短絡している場合に短絡電流を計算するために使用されるB側の抵抗

このプロパティはTyphoonSimではサポートされていません。値を変更してもTyphoonSimのシミュレーションにはまったく影響しません。

- パブリック - パブリックとしてマークされたコンポーネントは、すべてのレベルでシグナルを公開します。

- 保護済み - 保護済みとしてマークされたコンポーネントは、最初のロックされた親コンポーネントの外部のコンポーネントへの信号を非表示にします。

- 継承 - 継承としてマークされたコンポーネントは、継承以外の値に設定されている最も近い親の 'signal_access' プロパティ値を取得します。